# **MAINTENANCE INSTRUMENTATION**

# **PLC PROCESS AUTOMATION**

TRAINING MANUAL

Course EXP-MN-SI090

Revision 0

## **MAINTENANCE INSTRUMENTATION**

## **PLC PROCESS AUTOMATION**

#### **CONTENTS**

| 1. OBJECTIVES                                                   | _          |

|-----------------------------------------------------------------|------------|

| 2. INTRODUCTION TO AUTOMATION                                   | 9          |

| 2.1. WHAT IS AN AUTOMATED SYSTEM?                               | 9          |

| 2.2. EXPRESSION OF REQUIREMENTS FOR AN AUTOMATE                 | D SYSTEM11 |

| 2.2.1. First level                                              |            |

| 2.2.2. Second level                                             | 11         |

| 2.2.3. Third level                                              |            |

| 3. THE HARDWARE PART: THE PLC                                   |            |

| 3.1. EXTERNAL APPEARANCE OF THE PLC                             | 13         |

| 3.2. DEFINITIONS                                                | 14         |

| 3.3. STRUCTURE OF A PLC                                         | 14         |

| 3.3.1. The base                                                 |            |

| 3.3.2. Power supply                                             |            |

| 3.3.3. The Input / Output boards                                |            |

| 3.3.3.1. The digital input board                                |            |

| 3.3.3.2. The digital output board                               | 16         |

| 3.3.3.3. The analog input board                                 |            |

| 3.3.3.4. The analog output board                                |            |

| 3.3.4. The Microprocessor                                       | 18         |

| 3.3.5. The communication board                                  |            |

| 4. HOW DOES A PLC FUNCTION?                                     |            |

| 4.1. MICROPROCESSOR OPERATION                                   |            |

| 4.1.1. Why use a microprocessor?                                |            |

| 4.1.2. Description and internal structure of the microprocessor |            |

| 4.1.2.1. Advantages                                             |            |

| 4.1.2.2. Drawbacks                                              |            |

| 4.1.2.3. Functional diagram                                     |            |

| 4.1.2.4. The CPU                                                |            |

| 4.1.2.5. The program memory                                     |            |

| 4.1.2.6. The data memory                                        |            |

| 4.1.2.7. The parallel interface                                 |            |

| 4.1.2.8. The serial interface                                   |            |

| 4.1.2.9. The ADC (Analog-to-Digital Converter)                  | 29         |

| 4.1.2.10. The Timer                                             |            |

| 4.1.2.11. The Watch Dog                                         |            |

| 4.1.2.12. The clock signals                                     |            |

| 4.1.2.13. The exchange bus                                      | 30         |

| 4.2. HOW IS THE PROGRAM PROCESSED IN THE PLC?                   |            |

| 4.3. HOW THE PLC'S INPUT/OUTPUT BOARDS FUNCTION                 |            |

| 4.3.1. Logic inputs operation                                   |            |

| 4.3.2. Logic outputs operation                                  |            |

| 4.3.3. Passive or active input / output board?                  | 37         |

|    | 4.3.4. How does the PLC address the input/output signals? |       |

|----|-----------------------------------------------------------|-------|

| 5. | THE SOFTWARE PART                                         | .39   |

|    | 5.1. INTRODUCTION                                         | .39   |

|    | 5.1.1. History of programming languages                   | .39   |

|    | 5.1.2. The IEC 61131-3 standard                           | .42   |

|    | 5.2. LADDER LANGUAGE (LD)                                 | .42   |

|    | 5.2.1. Introduction                                       | .42   |

|    | 5.2.2. Instructions on bits                               | .45   |

|    | 5.2.2.1. The tests (contacts)                             | .45   |

|    | 5.2.2.2. Series contacts                                  |       |

|    | 5.2.2.3. Parallel contacts                                |       |

|    | 5.2.2.4. Writing (coils)                                  |       |

|    | 5.2.2.5. Network jumps and comments                       |       |

|    | 5.2.3. Instruction on words                               |       |

|    | 5.2.3.1. The tests (comparisons)                          |       |

|    | 5.2.3.2. The assignments (OPERATE)                        |       |

|    | 5.2.3.3. The combinatorial functions                      |       |

|    | 5.2.3.4. The bistable and pulse functions                 |       |

|    | 5.2.4. Example of a complete program                      | .52   |

|    | 5.3. FUNCTION BLOCK DIAGRAM (FBD) LANGUAGE                |       |

|    | 5.3.1. The Functions                                      |       |

|    | 5.3.2. The standard functions                             |       |

|    | 5.3.2.1. The conversion functions                         |       |

|    | 5.3.2.2. The numerical functions                          |       |

|    | 5.3.2.3. The selection and limitation functions           |       |

|    | 5.3.2.4. The comparison functions                         |       |

|    | 5.3.2.5. The functions on character strings               |       |

|    | 5.3.2.6. The date and time functions                      |       |

|    | 5.3.3. The function blocks                                |       |

|    | 5.3.3.1. Flip-flops                                       |       |

|    | 5.3.3.2. Edge detection                                   |       |

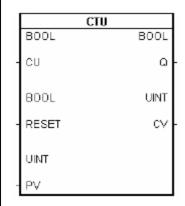

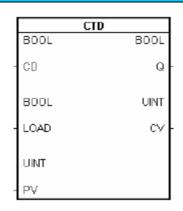

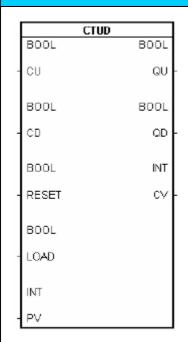

|    | 5.3.3.3. Counters                                         |       |

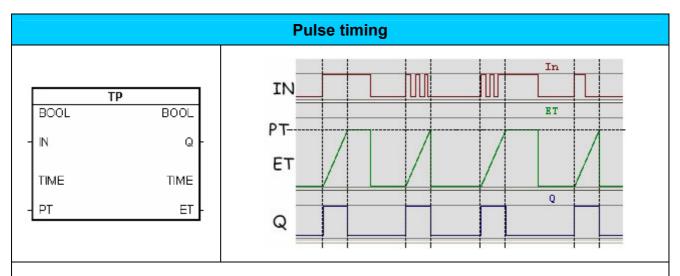

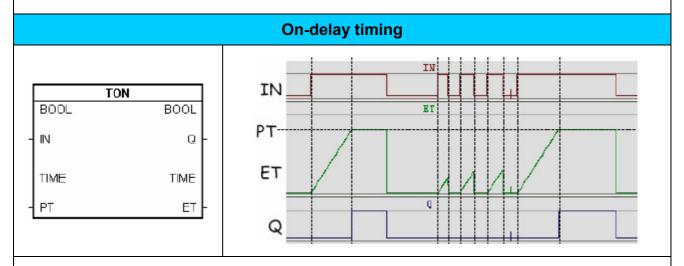

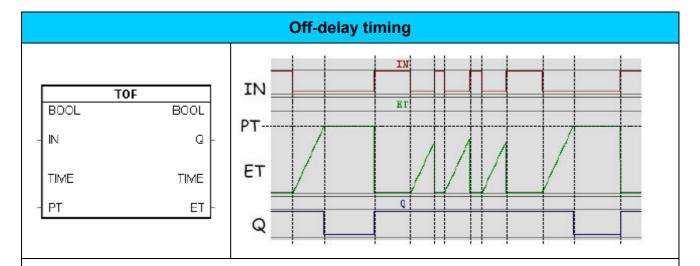

|    | 5.3.3.4. The timers                                       |       |

|    | 5.3.3.5. Library and function blocks                      |       |

|    | 5.3.4. Conclusion                                         |       |

|    | 5.4. THE SEQUENTIAL FUNCTION CHART LANGUAGE (SFC)         |       |

|    | 5.4.1. Definitions                                        |       |

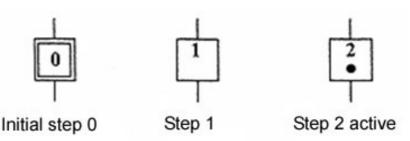

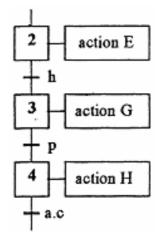

|    | 5.4.1.1. The steps                                        |       |

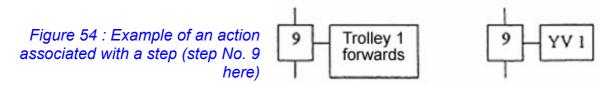

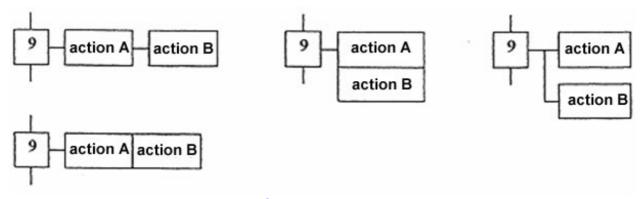

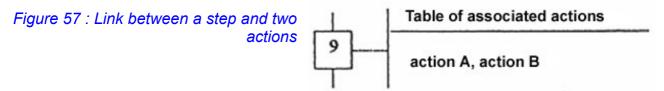

|    | 5.4.1.2. Actions associated with the step                 |       |

|    | 5.4.1.3. Transition                                       |       |

|    | 5.4.1.4. Receptivity associated with the transition       |       |

|    | 5.4.1.5. Oriented links                                   |       |

|    | 5.4.1.6. Using references in the links                    |       |

|    | 5.4.2. Syntax rule                                        |       |

|    | 5.4.3. Evolution rules                                    |       |

|    | 5.4.3.1. RULE 1: Initial Situation                        |       |

|    | 5.4.3.2. RULE 2: passing a transition                     |       |

|    | 5.4.3.3. RULE 3: Evolution of the active steps            | . / 4 |

| 5.4.3.4. RULE 4: Simultaneous evolutions                                      | 74  |

|-------------------------------------------------------------------------------|-----|

| 5.4.3.5. RULE 5: Simultaneous activation and deactivation                     |     |

| 5.4.3.6. RULE 6: Passing times for a transition or for a step's activity      |     |

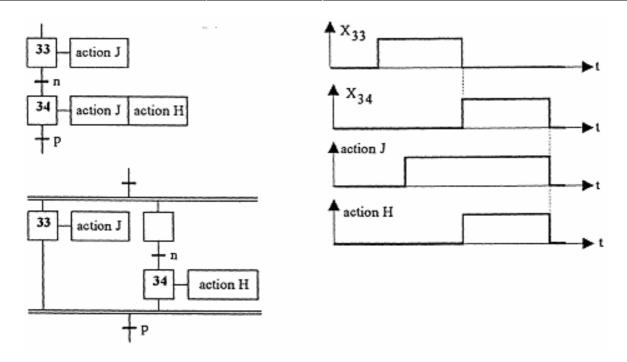

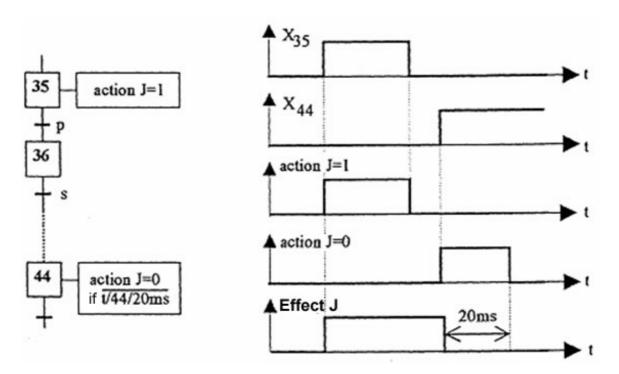

| 5.4.4. Detailed description                                                   |     |

| 5.4.4.1. Detailed description of the actions                                  |     |

| 5.4.5. Classification of actions                                              |     |

| 5.4.5.1. Continuous action                                                    |     |

| 5.4.5.2. Conditional action                                                   |     |

| 5.4.5.3. Delayed action                                                       |     |

| 5.4.5.4. Maintained effect                                                    |     |

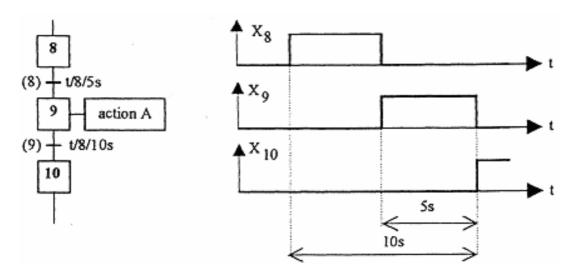

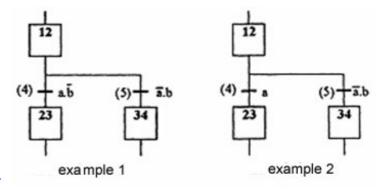

| 5.4.6. Detailed description of the receptivities                              |     |

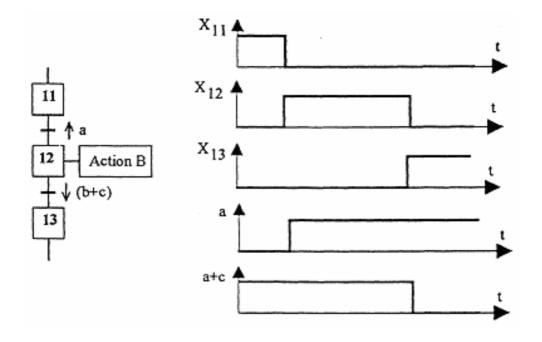

| 5.4.6.1. Taking time into account                                             |     |

| 5.4.6.2. Taking changes of information state into account                     |     |

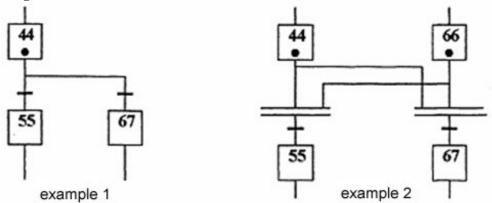

| 5.4.7. Unique sequence                                                        |     |

| 5.4.8. Sequence selection                                                     |     |

| 5.4.9. Exclusive sequences                                                    |     |

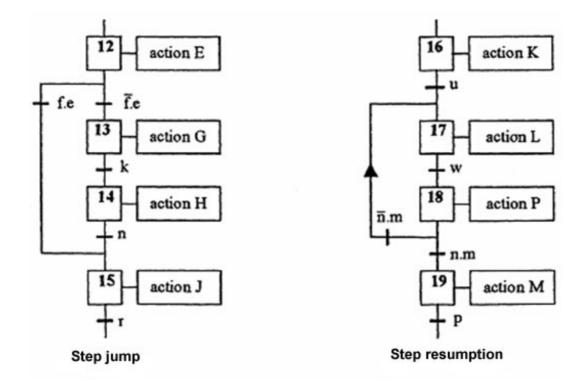

| 5.4.10. Step jumps and sequence resumptions                                   |     |

| 5.4.11. Simultaneous sequences: structural parallelism                        |     |

| 5.4.12. Interpreted parallelism                                               | 85  |

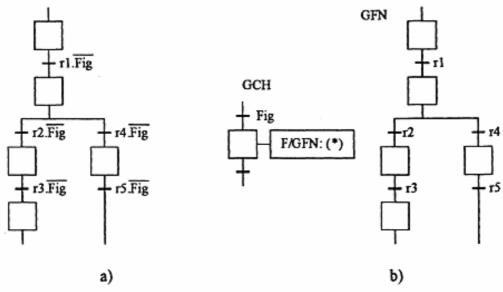

| 5.4.13. Reusing a given sequence                                              |     |

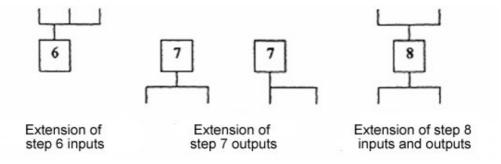

| 5.4.14. Macrosteps                                                            |     |

| 5.4.15. Sharing of resources or of sequences                                  | 87  |

| 5.4.16. Coupling between sequences                                            |     |

| 5.4.17. Rules for transforming a Sequential Function Chart into equations     |     |

| 5.4.17.1. Unique branch                                                       | 89  |

| 5.4.17.2. Divergence in OR                                                    |     |

| 5.4.17.3. Convergence in OR                                                   | 90  |

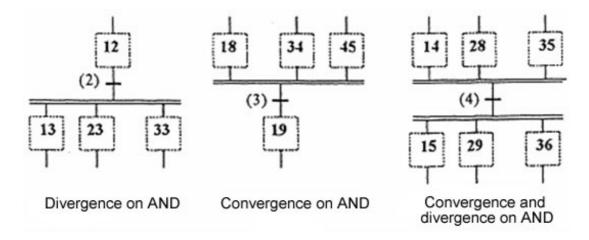

| 5.4.17.4. Divergence in AND                                                   |     |

| 5.4.17.5. Convergence in AND                                                  |     |

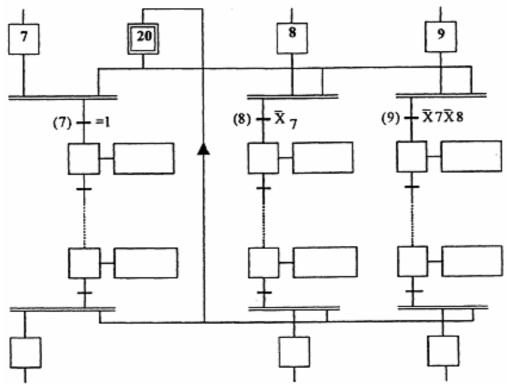

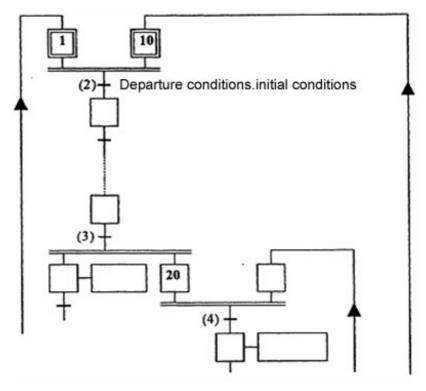

| 5.4.18. Organisation of Sequential Function Charts in RS memory: asynchronous | S   |

| sequencers                                                                    | 91  |

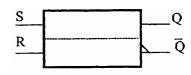

| 5.4.18.1. Reminder concerning RS memories                                     |     |

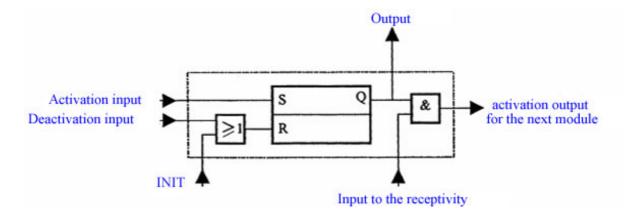

| 5.4.18.2. Creating a phase module                                             |     |

| 5.4.19. Problems encountered in asynchronous sequencers                       |     |

| 5.4.20. Organisation as a JK flip-flop: synchronous sequencers                |     |

| 5.4.21. The forcing orders                                                    |     |

| 5.4.21.1. Introduction                                                        |     |

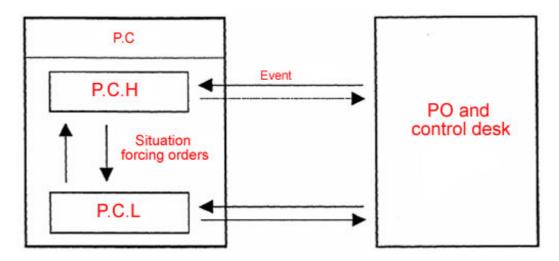

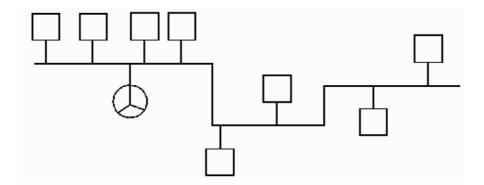

| 5.4.21.2. Hierarchical representation of the command part                     |     |

| 5.4.21.3. Hierarchical forcing order                                          |     |

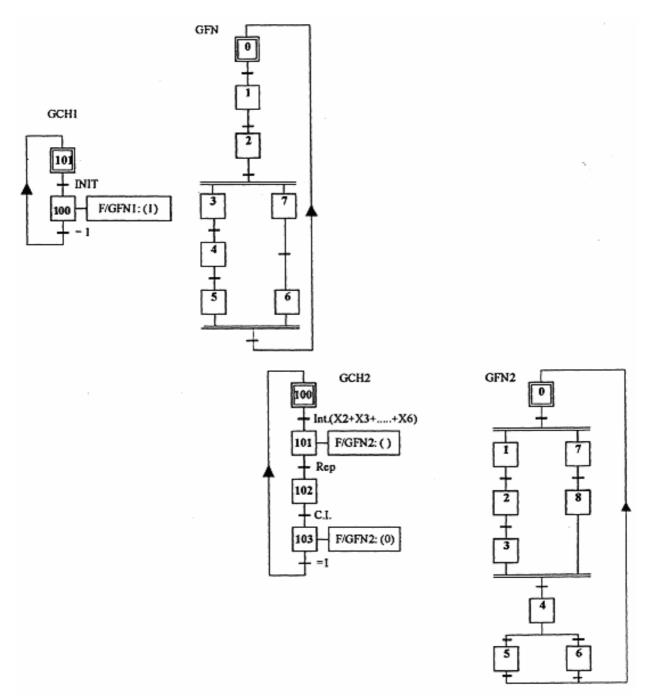

| 5.4.21.4. Hierarchical description by Sequential Function Chart               |     |

| 5.4.22. Special case of forcing: freezing                                     |     |

| 5.4.22.1. Conclusion on forcing and freezing orders                           |     |

| 5.4.23. Application to the special case of On and Off modes                   |     |

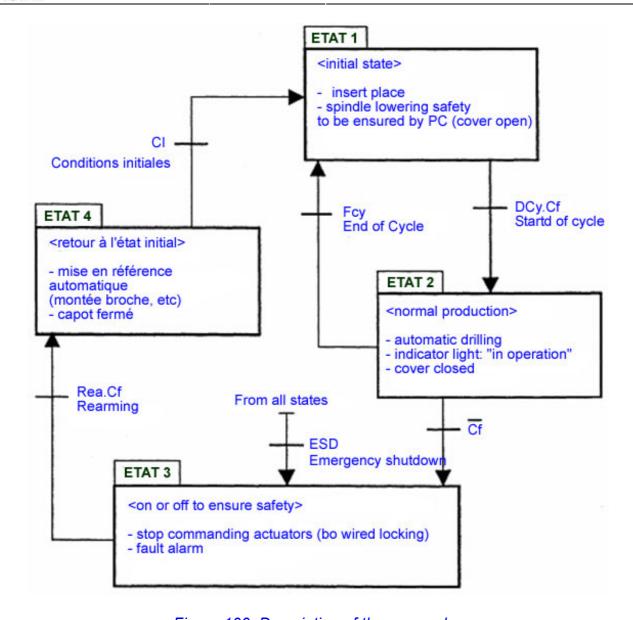

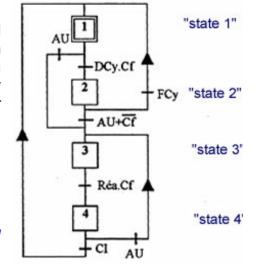

| 5.4.23.1. Analysis of an automated piece of equipment's run modes             |     |

| 5.4.23.2. Sequential Function Chart and run modes                             |     |

| 5.5. INSTRUMENT LIST (IL) LANGUAGE                                            |     |

| 5.5.1. Instructions                                                           |     |

| 5.5.1.1. Modifier                                                             | 107 |

|    | 5.5.2. Using functions                           | 108 |

|----|--------------------------------------------------|-----|

|    | 5.5.3. Using functional blocks                   |     |

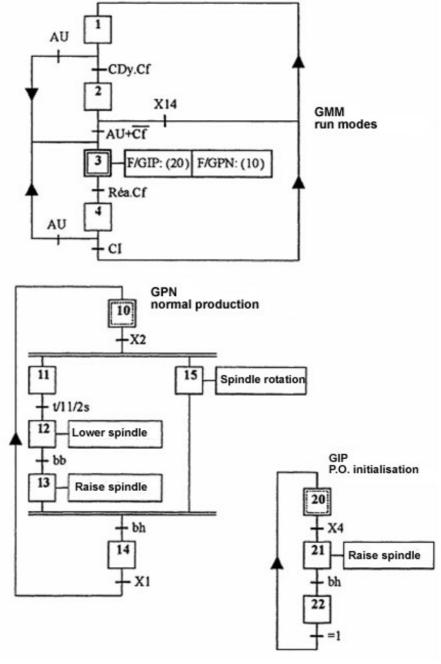

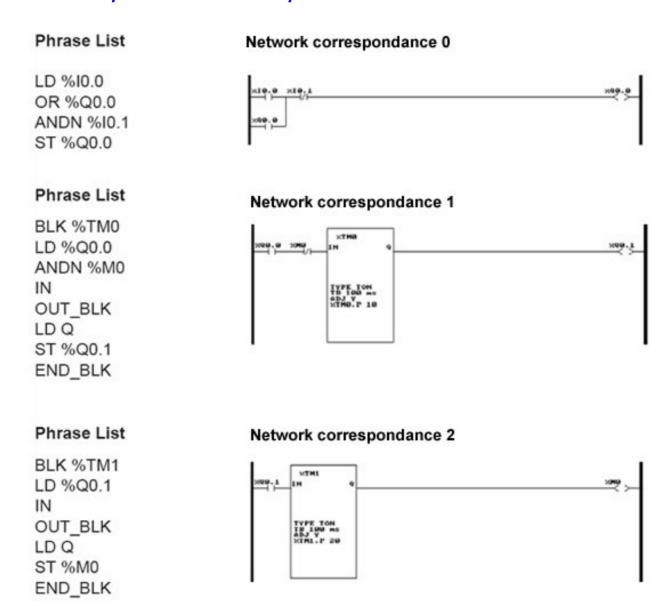

|    | 5.5.4. Examples of Ladder correspondence in List |     |

|    | 5.6. STRUCTURED TEXT LANGUAGE (ST)               |     |

|    | 5.6.1. The operators                             |     |

|    | 5.6.2. The control structures                    | 112 |

|    | 5.6.2.1. Conditional instructions                |     |

|    | 5.6.2.2. Choice instructions                     |     |

|    | 5.6.2.3. Repetitive instructions                 |     |

|    | 5.6.2.4. EXIT instruction                        |     |

|    | 5.6.2.5. RETURN instruction                      |     |

|    | 5.6.3. Using functions                           |     |

|    | 5.6.4. Using functional blocks                   |     |

| 6. | INDUSTRIAL LOCAL AREA NETWORKS                   | 116 |

|    | 6.1. THE INFORMATION TRANSMISSION TECHNIQUES     |     |

|    | 6.1.1. Connection techniques                     |     |

|    | 6.1.1.1. Single-wire connection                  | 119 |

|    | 6.1.1.2. Two-wire connection with chassis ground |     |

|    | 6.1.1.3. Differential two-wire connection        |     |

|    | 6.1.2. Baseband transmission                     |     |

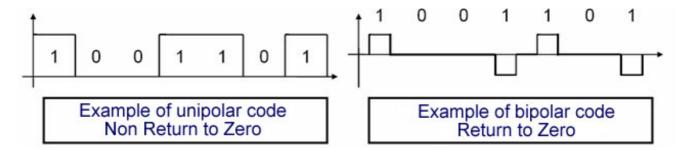

|    | 6.1.2.1. Polarities                              | 121 |

|    | 6.1.2.2. Asynchronous codes                      | 122 |

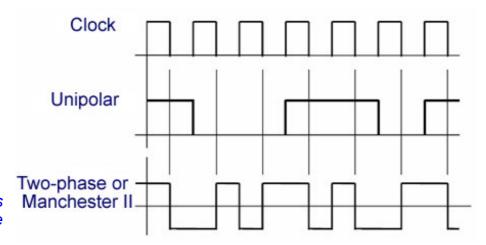

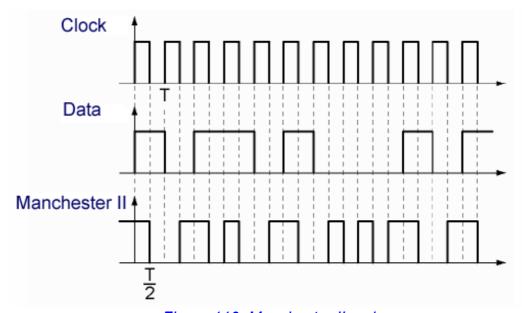

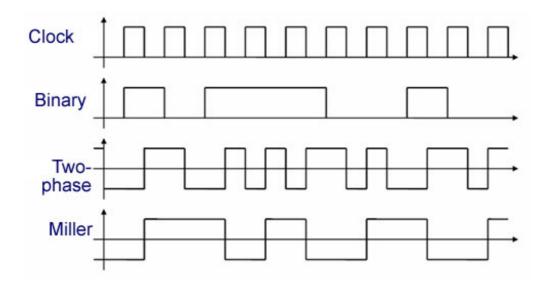

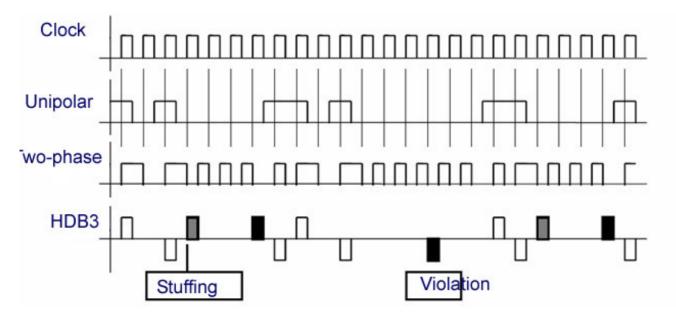

|    | 6.1.2.3. Synchronous codes                       |     |

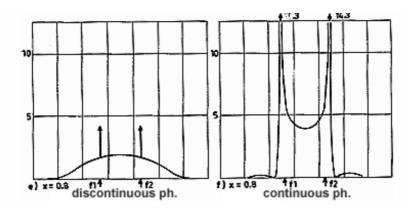

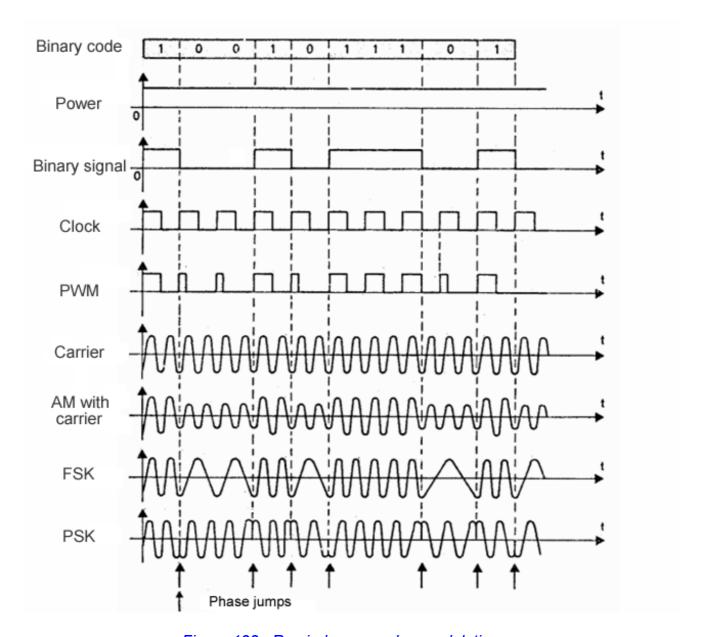

|    | 6.1.3. Band shift transmission                   | 126 |

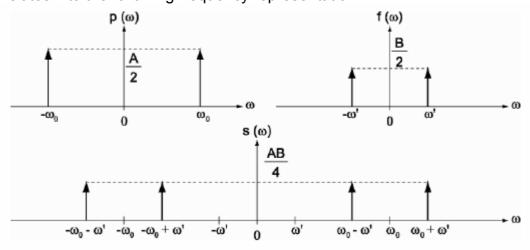

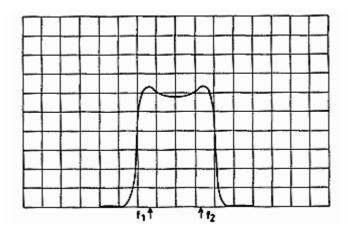

|    | 6.1.3.1. Amplitude modulations                   | 127 |

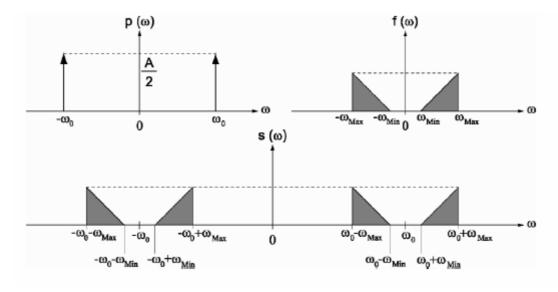

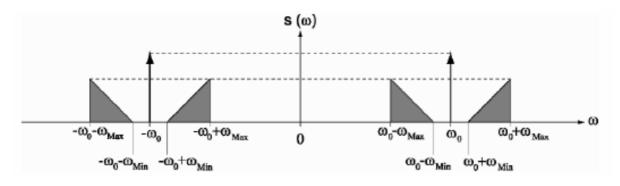

|    | 6.1.3.2. The different amplitude modulations     | 129 |

|    | 6.1.3.3. Angle modulations                       |     |

|    | 6.1.3.4. Reminders on analog modulations         | 136 |

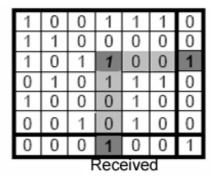

|    | 6.1.4. Information coding                        | 137 |

|    | 6.1.4.1. Parity coding                           |     |

|    | 6.1.4.2. Redundant coding                        |     |

|    | 6.1.4.3. CRC codes                               |     |

|    | 6.1.5. Correction of transmission errors.        | 142 |

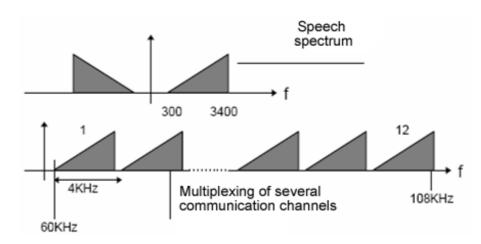

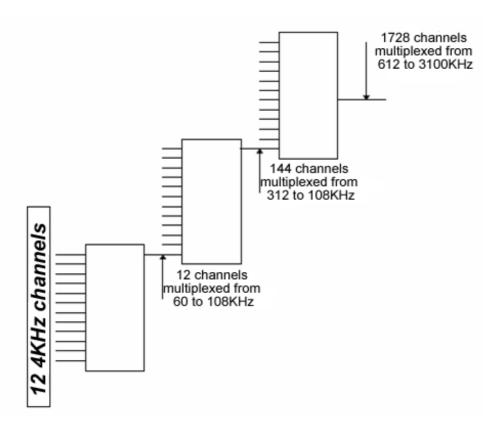

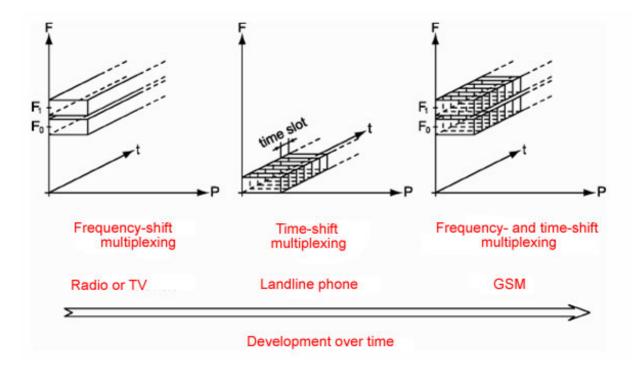

|    | 6.1.6. Multiplexing                              |     |

|    | 6.1.6.1. Frequency-division multiplexing         |     |

|    | 6.1.6.2. Time-division multiplexing              |     |

|    | 6.1.7. Transmissions vocabulary                  |     |

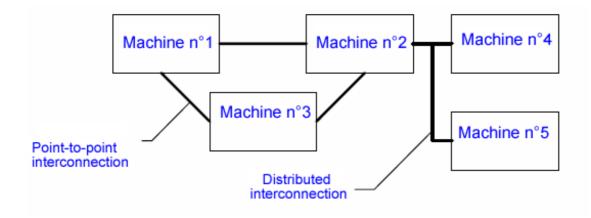

|    | 6.2. THE FIRST COMPUTER NETWORKS                 |     |

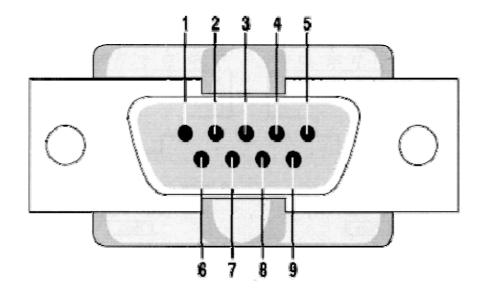

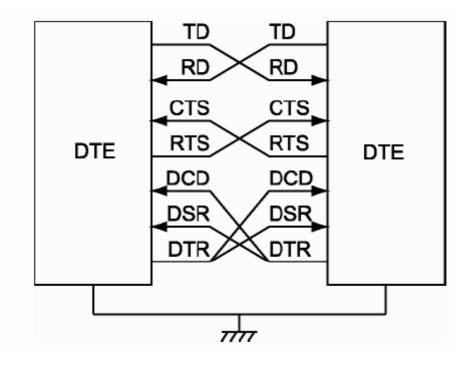

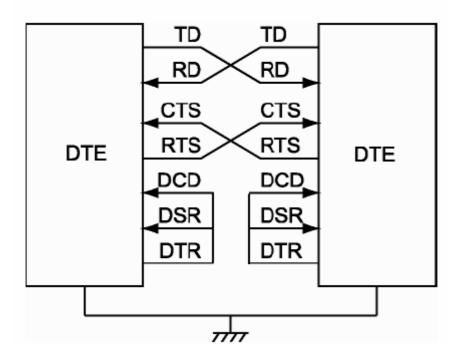

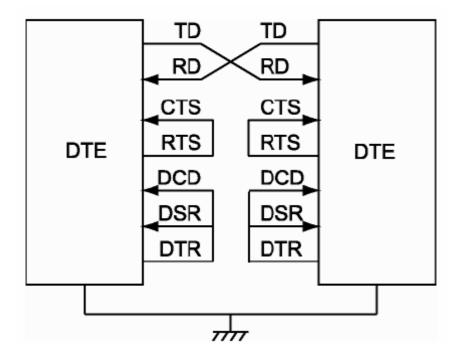

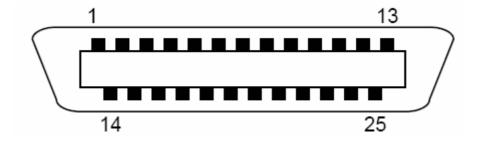

|    | 6.2.1. The RS232 standard                        |     |

|    | 6.2.1.1. Presentation.                           |     |

|    | 6.2.1.2. Flow control                            |     |

|    | 6.2.2. The IEEE 488 bus                          |     |

|    | 6.2.2.1. Machine control signals                 |     |

|    | 6.2.2.2. HAND-SHAKE (flow control):              |     |

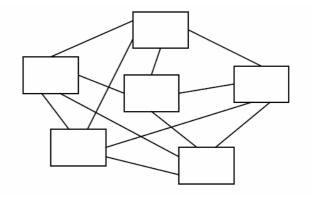

|    | 6.3. NETWORK ORGANISATION                        |     |

|    | 6.3.1. The OSI standard                          |     |

|    | 6.3.1.1. The 7 layers of the OSI standard        |     |

|    | 6.3.1.2. Data encapsulation                      | 163 |

|    | 6.3.2. Frames and packets                                |     |   |

|----|----------------------------------------------------------|-----|---|

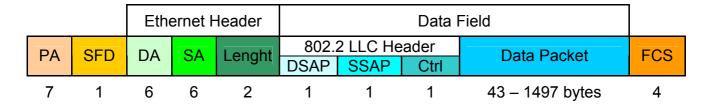

|    | 6.3.2.1. Principle of the basic frame                    | .16 | 4 |

|    | 6.3.2.2. Principle of the packet                         | .16 | 4 |

|    | 6.4. THE PHYSICAL LAYER                                  |     |   |

|    | 6.4.1. Network topology                                  | .16 | 5 |

|    | 6.5. THE MEDIUM                                          |     |   |

|    | 6.5.1. Remark on propagation speeds                      |     |   |

|    | 6.5.2. Twisted pairs                                     |     |   |

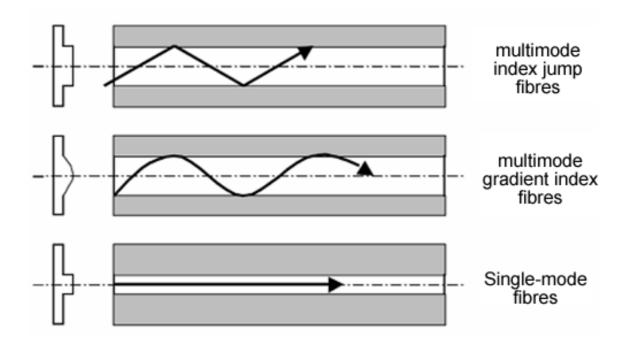

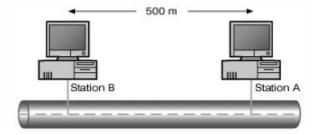

|    | 6.5.3. Optical fibres                                    |     |   |

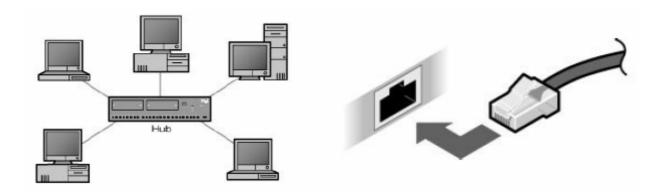

|    | 6.5.4. The elements making up the physical layer         |     |   |

|    | 6.6. ETHERNET                                            |     |   |

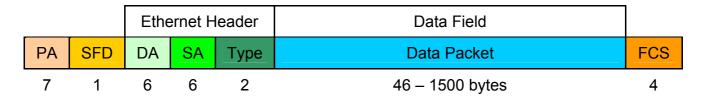

|    | 6.6.1. Fundamental frame                                 |     |   |

|    | 6.6.1.1. The preamble                                    |     |   |

|    | 6.6.1.2. The destination and source addresses            |     |   |

|    | 6.6.1.3. The type                                        |     |   |

|    | 6.6.1.4. The data field                                  |     |   |

|    | 6.6.1.5. Table of Ethertypes.                            |     |   |

|    | 6.6.2.                                                   |     |   |

|    | 6.6.3. Ethernet's Physical layer                         |     |   |

|    | 6.6.4. The Ethernet link layer                           |     |   |

|    | 6.7. THE DATA TRANSMISSION PROTOCOLS                     |     |   |

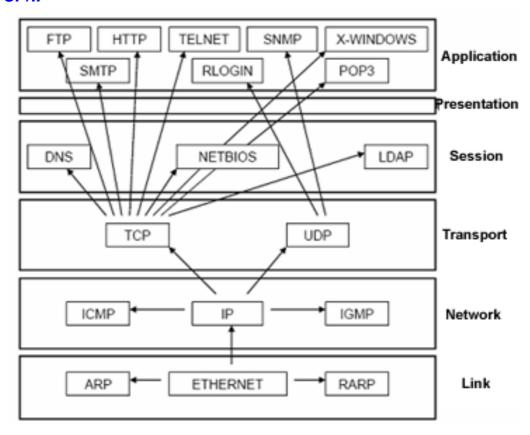

|    | 6.7.1 TCP/IP                                             |     |   |

|    |                                                          |     |   |

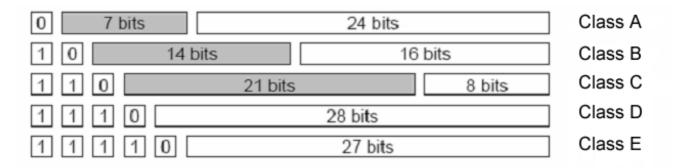

|    | 6.7.2. The IP protocol                                   |     |   |

|    | 6.7.3. The IP frame's options                            |     |   |

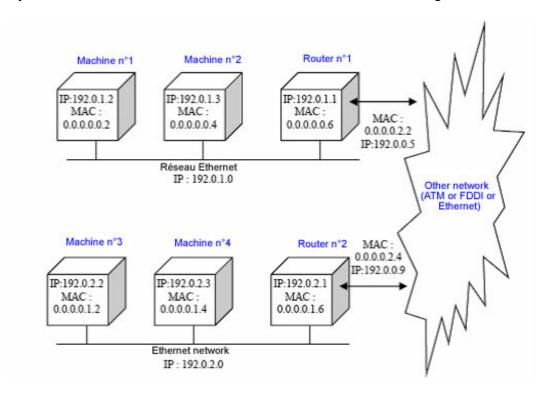

|    | 6.7.4. IP and Ethernet                                   |     |   |

|    | 6.7.5. The PING command                                  |     |   |

|    | 6.7.6. IP operation                                      |     |   |

|    | 6.7.6.1. Identification of the local addresses           |     |   |

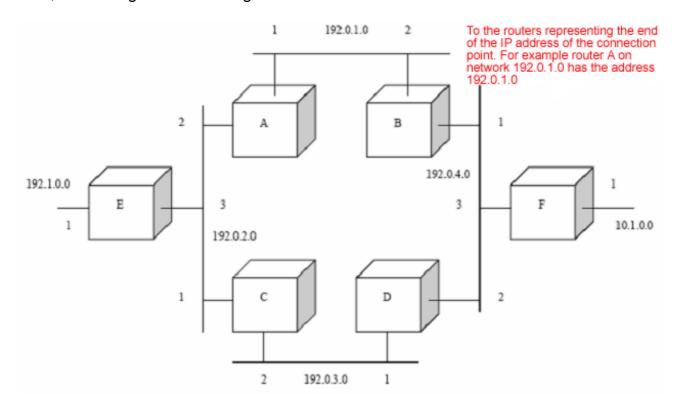

|    | 6.7.7. Routing of the IP packets                         |     |   |

|    | 6.7.7.1. The RIP protocol                                |     |   |

|    | 6.7.7.2. Distribution and constitution of the RIP tables |     |   |

|    | 6.7.7.3. The RIP frame                                   | _   | _ |

|    | 6.7.8. The MODBUS protocol                               |     |   |

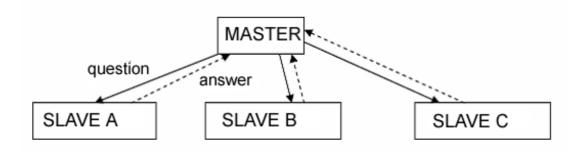

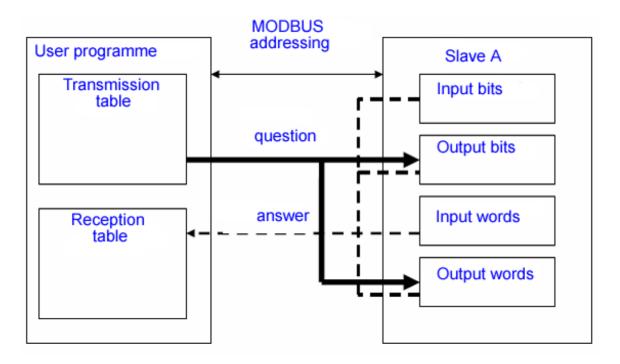

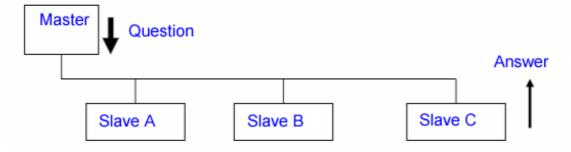

|    | 6.7.8.1. Principle of MODBUS exchanges                   |     |   |

|    | 6.7.8.2. Addressing                                      |     |   |

|    | 6.7.8.3. Exchange from master to one slave               |     |   |

|    | 6.7.8.4. Exchange from master to all the slaves          |     |   |

|    | 6.7.8.5. Question/answer exchange frame                  |     |   |

|    | 6.7.8.6. General frame format                            |     |   |

|    | 6.7.8.7. Transmission medium                             |     |   |

|    | 6.7.9. The PROFIBUS protocol                             |     |   |

|    | 6.7.9.1. Profibus DP                                     |     |   |

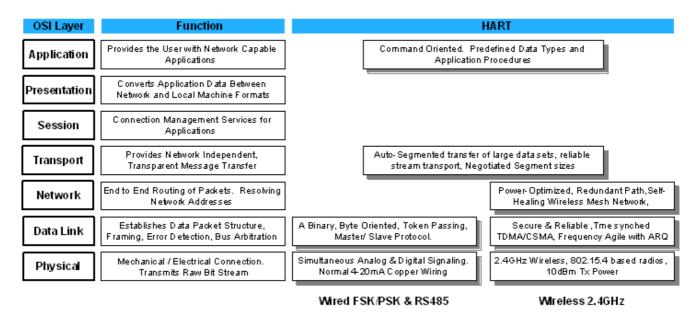

|    | 6.7.10. The HART protocol                                | .20 | 9 |

|    | 6.7.10.1. What is HART?                                  |     |   |

|    | 6.7.10.2. How does HART function?                        | .21 | 1 |

|    | 6.7.10.3. The HART specifications                        | .21 | 4 |

|    | 6.7.10.4. What is contained in HART data?                |     |   |

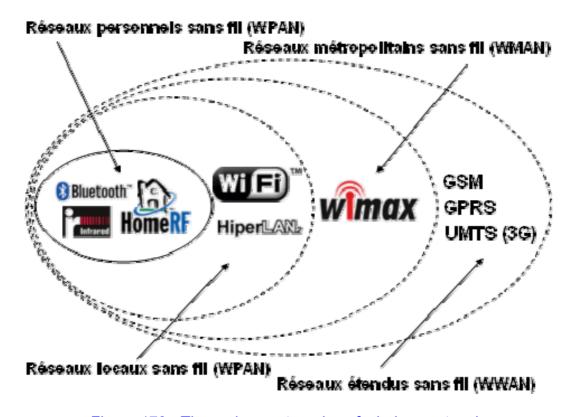

| 7. | THE WIRELESS NETWORK                                     | .21 | 8 |

|    |                                                          |     |   |

| 7.1. INTRODUCTION                          | 218 |

|--------------------------------------------|-----|

| 7.1.1. What is a wireless network?         | 218 |

| 7.1.2. The categories of wireless networks | 219 |

| 7.2. Wi-Fi                                 |     |

| 7.2.1. Presentation                        | 219 |

| 7.2.2. The different Wi-Fi standards       | 221 |

| 7.2.3. Ranges and speeds                   | 223 |

| 7.2.3.1. The 802.11a standard              |     |

| 7.2.3.2. The 802.11b standard              | 224 |

| 7.2.3.3. The 802.11g standard              | 225 |

| 8. LIST OF FIGURES                         |     |

| 9. LIST OF TABLES                          | 230 |

## 1. OBJECTIVES

The purpose of this course is to ensure the future instrumentation specialist has a basic knowledge of process automation (via Programmable Logic Control - PLC) on a predominantly oil-oriented industrial site.

## 2. INTRODUCTION TO AUTOMATION

#### 2.1. WHAT IS AN AUTOMATED SYSTEM?

An industrial process consists of a set of equipment that makes it possible, using power and raw materials or unfinished products, to manufacture finished products or directly usable objects. The automation of a process means placing it under the control and command of a system that leads towards a given goal despite the disturbances it is submitted to.

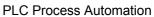

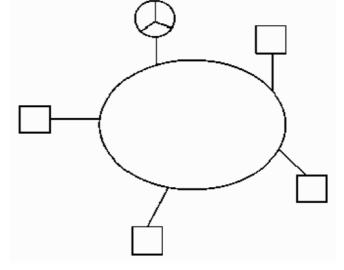

An automated system consists of three parts:

- The industrial process (called the operative part),

- The control or command system (called the command part),

- The operator

Figure 1: General description of an automated system

**The operative part** performs the operations by means of actuators (motor, cylinder, etc.)

It receives orders from the command part.

It sends reports to the command part.

<u>The command part</u> receives its **instructions** from the operator and reports from the operative part.

It sends **orders** to the operative part and signals to the operator.

It is the command part's **program** that manages all these exchanges of information.

<u>The operator</u> is a person who gives instructions to the system and who is capable of understanding the signals that the command part returns to him/her.

#### The industrial process consists of:

- Production and distribution of electrical power (hydro-electrical, thermal or nuclear power station, remote management of network control),

- ♣ Treatment of fluids (extraction, transport and refining of oil) or of minerals (mines, steel industry, cement works, etc.),

- Transformation of metals or chemicals.

- Manufacture of miscellaneous products (paper, plastic),

- Production of manufactured parts and their assembly to make machines,

- ♣ Manufacture of objects and products useful for man's work and leisure,

- Manufacture, processing and packaging of food produce,

- ♣ Transport infrastructures (sea or river ports, national or urban rail networks, motorways, airports).

## The control-command system consists of:

- Information sensors that measure all the physical values required to monitor and command the correct operation of the automated system; they transform movements, flow rates, pressures, temperatures, levels into electrical signals. They involve several technologies, sometimes certain sensors are automated and we call them analysers (ph-meter, chromatograph, spectrograph, densimeter, refractometer, etc....).

- Information processing circuits which create the command orders, the information signals that they process may be in their original form, in which case we say that processing is analog (case of regulators, synchro systems, etc.); but these signals may also be converted into binary number coded form (analog-to-digital conversion) and then processed by a computer or by a Programmable Logic Controller (PLC) and then processing is said to be digital.

- ♣ Actuators that perform the actions and make the physical interventions that the command system imposes on the industrial process. These actuators belong to the following three technologies: electrical (motors, generators, pump or valve commands, etc.), pneumatic (valves, cylinders, etc.), hydraulic (cylinders, hydraulic motors, brakes, etc.).

#### 2.2. EXPRESSION OF REQUIREMENTS FOR AN AUTOMATED SYSTEM

In order to enable the dialogue between the automated system's designer-manufacturer and the user-customer of the automated system, to arrive at a clear and unambiguous description of the hardware, to take into account the technical limitations and operating restrictions, you will have to write a document specifying all the functions, all the values, the physical magnitudes and all the utilisation modes for the hardware that the two parties want to obtain.

When you look at a problem for the first time, some things are not clear and a host of details may make you forget important events. It is recommended to divide up and spread the description of the hardware over several – at least three – levels.

#### 2.2.1. First level

This corresponds to the functional specifications that describe the automated system through its functioning coupled with the process, independently from the technique used.

These specifications must enable the designer of the automated system to understand its role (the functions), define the actions to be performed and their sequencing. All the triangular exchanges of information and energy between the automated system, the process and the outside world, all the functional safety systems must be described at this level.

#### 2.2.2. Second level

This corresponds to the technical specifications and operational specifications which indicate the way the exchanges of information and energy are made between the automated system and the process.

The technical specifications list and explain all the information on the nature and physical characteristics of the sensors, actuators and electronic circuits (constraints, performance, limitations), to which we add the environmental conditions (temperature, humidity, corrosive or explosive atmosphere, electrostatic or electromagnetic disturbances, etc.) and the reliability conditions required to ensure operating safety.

The operational specifications indicate in a very practical way how the complete automated system is implemented (sensors, actuators, control-command) in its operating context: availability between two successive maintenance operations, ease of modification, troubleshooting, On-Off modes, absence of dangerous failures.

#### 2.2.3. Third level

This concerns the documentation describing the functioning, utilisation, maintenance and troubleshooting of the hardware. This documentation must be constantly updated gradually as modifications are made. This will make it possible to simplify the maintenance and troubleshooting operations

## 3. THE HARDWARE PART: THE PLC

PLCs (Programmable Logic Controller) appeared in the United States in about 1969 where they were developed to satisfy the desire of industry to set up automated manufacturing and production lines that could follow the changes in the techniques used and in the models manufactured.

A PLC differs from a calculator in that it is a programmable electronic system specially designed for non-IT specialists. In general it is designed to be placed in the hands of personnel whose training has above all been oriented towards instrumentation and automation.

PLCs have taken the place of relay boxes because of their flexibility (putting into service, modification, etc.), and also because in complex command automated systems, the costs of wiring and debugging were becoming prohibitive.

#### 3.1. EXTERNAL APPEARANCE OF THE PLC

PLCs are available in modular form (different types of microprocessors and inputs-outputs) and various presentations: case, rack, bay or boards.

For difficult atmospheres (temperature, dust, risk of projections, etc.) the PLCs used are contained in a sealed box, capable of withstanding a broad temperature range.

The constraints of the industrial environment take three forms:

- physical and mechanical environment;

- chemical pollution;

- electrical disturbances.

#### 3.2. DEFINITIONS

In France these pieces of equipment are called **API** (Automate **P**rogrammable **I**ndustriel), and in the United States, **PLC** (**P**rogrammable **L**ogic **C**ontrollers).

#### 3.3. STRUCTURE OF A PLC

Figure 2: SIEMENS S7-400 PLC

#### 3.3.1. The base

The base is quite simply the rack in which you plug in all your input-output boards, the power supply board, the CPU board (microprocessor associated with the memory) and, lastly, your communication board.

Figure 3: A base rack

Training Manual EXP-MN-SI090-EN Last revised on: 17/12/2008

The base is very practical because the PLC's power supply is distributed to all the modules connected to this backpanel base, so you only need one power supply (via the power supply board).

It is attached to a cabinet chassis by means of its DIN rail.

There are several base variants which are defined according to the number of modules to be interconnected on it (e.g. 9 or 18 modules maximum per base).

The bases are attached in cabinets that we call 19-inch bays. Opposite you can see an example of a bay:

Figure 4: Example of a PLC bay

In the DCS Centralised Automation course, we will see that we can also install servers in this type of bay.

## 3.3.2. Power supply

The power supply board is used to power all of the PLC's boards installed in the base. This type of board is most often powered with 24 VDC via a stabilised filtered 230VAC/24VDC power supply.

You must always use a 230VAC power outlet taken from the uninterruptible power supply to power a PLC.

Figure 5: Various power supply boards

You will see that there is a battery on the power supply board, and above all don't take it to power your TV remote control, the PLC needs these batteries. We will see what they are really used for in the PLC Description and Operation chapter.

## 3.3.3. The Input / Output boards

## 3.3.3.1. The digital input board

The digital input board will allow us to monitor all the logic inputs of the following types:

- ♣ Valve end-of-travel,

- Pushbutton,

- Motor operating feedback,

- Pressure switch,

- Thermostat.

- Level detector,

- Etc.

Figure 6: Digital input board

These Digital Input boards may have 8, 16 or 32 channels.

They are equipped with LEDs which indicate to us the logic status of the inputs assigned on the board.

## 3.3.3.2. The digital output board

The digital output board allows us to command all actuators of the following types:

- Solenoid valve,

- Motor command,

- Indicator light,

- **♣** Etc.....

Figure 7: Digital output board

Digital Output boards may have 8, 16 or 32 channels. They also have LEDs indicating the logic state of the outputs assigned on the board.

## 3.3.3.3. The analog input board

The analog input board will allow us to have all the measurements of the following types in the PLC:

- Pressure,

- Flow rate,

- Temperature,

- Level,

- Etc.

Figure 8: Analog input board

Analog Input boards may have 4, 8 or 16 channels.

## 3.3.3.4. The analog output board

The analog output board will allow us to regulate all the following actuators:

- Regulation valve,

- Speed variator,

- Etc.

Figure 9: Analog output board

Analog Output boards may have 4, 8 or 16 channels.

You must take care, because analog input and out boards look very much alike, you are therefore advised to examine carefully the references of the boards which are often indicated on each board.

Depending on the references, you can consult the manufacturer's documentation to check what type of board you are installing. Anyone can make a mistake!!!!.

## 3.3.4. The Microprocessor

The microprocessor is the PLC's brain, this is what is going to manage all the PLC's I/Os according to the program that has been installed in it. We will see exactly how it functions in the following chapters.

Figure 10: Microprocessor associated with a memory

Each CPU has a mode switch making it possible to change operating mode.

This is essentially a removable key switch that is used to switch between the RUN and STOP operating modes.

The following operating modes are possible:

| RUN-P<br>RUN<br>STOF MRES | RUN-P | To run the program<br>All the PG functions are enabled      |

|---------------------------|-------|-------------------------------------------------------------|

|                           | RUN   | To run the program Only the PG read functions are enabled   |

|                           | STOP  | The program is not run.<br>All the PG functions are enabled |

|                           | MRES  | Position in which you can perform a general memory reset.   |

Figure 11: A CPU's various operating modes

PG means Programming console.

## **General Reset:**

This function clears all the user data from the CPU. This must be performed once before starting to program the PLC (at the beginning of a project for example).

This is done in several steps:

| Step | Action                                                                                                                                       | Result                                                                                                                                                                                                                                         |

|------|----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | Place the operating mode switch in the <b>STOP</b> position                                                                                  | The STOP indicator light comes on                                                                                                                                                                                                              |

| 2    | Place the switch in the <b>MRES</b> position and hold it in that position (for about 3 seconds) until the STOP indicator light comes back on | The STOP indicator light goes out and after about 3 seconds it comes back on again.  For new CPU models, wait until the STOP indicator light comes on for the second time.  Important: you must not wait more 3 seconds between steps 2 and 3. |

| 3    | Return the switch to the STOP position and then back to the MRES position after 2 seconds                                                    | The STOP indicator light flashes for about 3 seconds and then comes on steady: everything is OK, <b>the general CPU reset</b> has been successful                                                                                              |

Table 1 : Steps for performing a general CPU reset

#### 3.3.5. The communication board

The communication board makes it possible to communicate in a network with several PLCs; we can connect up to a desktop PC to program the PLC via a coupler.

Figure 12: Communication board

It is also used by the maintenance technician who can connect his laptop PC to it to check what is not functioning correctly.

In the photograph you can see that there are two Ethernet ports, these will allow you to connect your PCs with an RJ45 network cable.

## 4. HOW DOES A PLC FUNCTION?

In this chapter, we are going to look at how the microprocessor (and therefore the CPU board) functions.

#### 4.1. MICROPROCESSOR OPERATION

#### 4.1.1. Why use a microprocessor?

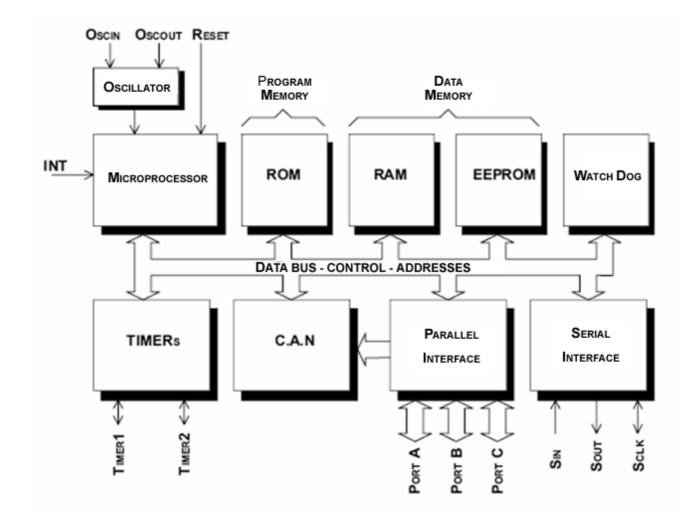

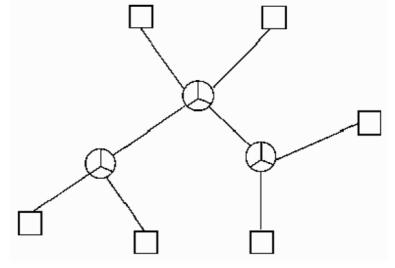

Figure 13: Microprocessor organisation

A technical object, integrating electronics, often has functions whose purpose is to process information: arithmetic (addition, multiplication, etc.) or logic (AND, OR, etc.) operations between several input signals making it possible to generate output signals.

These various functions can be performed by analog or digital integrated circuits.

But when the technical object becomes complex, and it is then necessary to perform a large amount of information processing operations, it is simpler to use a structure based on a *microprocessor*.

## 4.1.2. Description and internal structure of the microprocessor

A microprocessor takes the form of an integrated circuit combining all the following components:

- The processor often called CPU (Central Processing Unit),

- The data memory (RAM and EEPROM),

- ♣ The program memory (ROM, OTPROM, UVPROM or EEPROM),

- Parallel interfaces for connecting the Inputs / Outputs,

- ♣ Series interfaces (synchronous or asynchronous) for the dialogue with other units,

- Timers to generate or measure signals with a great time precision.

- Analog-to-Digital Converters for the processing of analog signals.

## 4.1.2.1. Advantages

- Small dimensions,

- Not very complex printed circuit,

- Low consumption,

- Low cost.

#### 4.1.2.2. **Drawbacks**

- System that is costly to develop,

- Programming requiring appropriate hardware.

#### 4.1.2.3. Functional diagram

The functional diagram below represents a "Von Neumann" architecture (common to all microprocessors) where the program memory shares the same bus as the data memory.

Figure 14: Functional diagram of a microprocessor

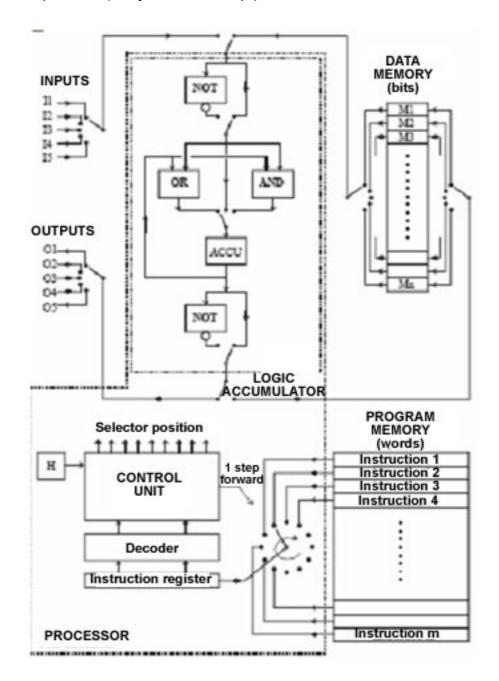

#### 4.1.2.4. The CPU

A microprocessor sequentially executes the instructions stored in the program memory (ROM). It is therefore capable of operating on binary words whose size in bits is that of the data bus (sometimes the double for certain microprocessors).

It is generally made up of the following elements:

- One or more accumulator registers temporarily containing the operands as well as the results of the operations,

- Auxiliary registers making it possible to relay the accumulators,

- Index registers for the indirect addressing mode,

- ♣ A program counter pointing to the address of the next instruction to be executed, its size is the same as that of the address bus,

- An Arithmetic Logic Unit (ALU) making it possible to perform operations between the accumulator and the operands,

- ♣ A condition code register indicating certain particularities concerning the result of the last operation (carry, zero, interrupt).

Figure 15: Detailed diagram of a microprocessor

As you can see in the figure above, the **logic unit** is associated with a data memory (which is bistable and made up of n bits) which is used to memorise the sequential information and store the intermediate results.

On the processor's **control unit** you also have a series of selectors that allow the logic operators, inputs, outputs and memories to establish communications.

**The logic accumulator** (ACCU) that is contained in the **logic unit** is a special type of memory cell which intervenes in a privileged way in the logic operations. It is also used to store the result obtained by the logic operation.

The processor's **control unit** manages overall operation under the control of the **instructions** stored in the program.

The **instructions** are sent in succession to the instruction register, and are then decoded and, according to the operations that they indicate, the control unit generates the orders required for their execution. This represents a **sequential and cyclic** execution of the program.

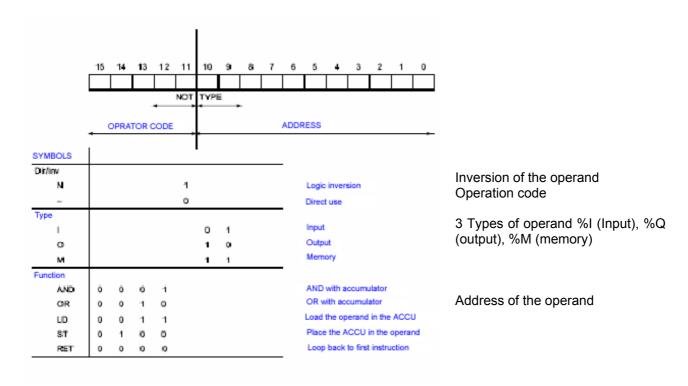

#### **Instruction format**

An instruction must provide all the indications required to execute the operation and it uses several bits forming a word.

Reminder: a word is made up of 16 bits. A byte is made up of 8 bits, so a word consists of two bytes.

In our instruction we can see that in our word we have 5 bits for the operator code and 11 bits for the address.

Figure 16: Instruction format

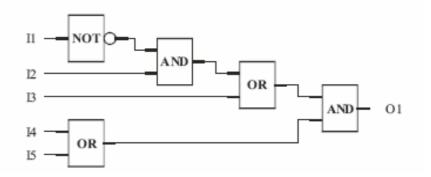

#### Example:

The output is O1, the inputs are I1, I2, I3, I4, I5

## O1 := (( NOT I1 AND I2) OR I3) AND ( I4 OR I5)

The list of instructions is as follows:

| 1 | LND I1                                           | Put inverted I1 in the ACCU                         |

|---|--------------------------------------------------|-----------------------------------------------------|

| 2 | AND I2                                           | And between ACCU and I2 <b>⊃</b> result in the ACCU |

| 3 | OR I3                                            | Or between ACCU and I3 Tesult in the ACCU           |

| 4 | ST M1                                            | Save ACCU in memory M1                              |

| 5 | LD I4                                            | Put I4 in the ACCU                                  |

| 6 | OR I5                                            | Or between ACCU and I5 Tesult in the ACCU           |

| 7 | 7 AND M1 And between ACCU and M1 To result in M1 |                                                     |

| 8 | ST 01                                            | Put the value of ACCU in output O1                  |

| 9 | RET                                              | Loop back to instruction No. 1                      |

In this example, we have an instruction in a textual language.

## 4.1.2.5. The program memory

This device contains the instructions for the program that the microprocessor must execute.

This type of memory, called Read Only Memory, can only be read-accessed.

A special and appropriate procedure is required to program this type of memory.

There are different types depending on their programming mode:

- ROM whose content is programmed when it is manufactured,

- PROM which is electrically programmable once only by the developer (also called OTPROM),

- EPROM which is electrically programmable and erasable by means of UV (also called UVPROM),

- EEPROM which is electrically programmable and erasable.

## 4.1.2.6. The data memory

This device is used to temporarily store the data generated by the microprocessor during the various digital processing phases (result of operations, sensor states, etc.). These memories are read- and write-accessible.

#### There are two types:

- Random Access Memory (RAM) (data lost if the power is cut out) with a relatively short read and write time (some nanoseconds),

- non-volatile read only memory (EEPROM) (data kept if the power is cut out) with a relatively long write time (some milliseconds) with respect to the read time which is quite short (some nanoseconds).

## 4.1.2.7. The parallel interface

This type of interface, distributed over several ports (8 bits maximum), makes it possible to take into account the logic states applied at input (sensor state) or to generate binary output signals (actuator commands).

The pins of these ports can be configured as input or output, with different options (pull-down resistors, open collector outputs, interrupt, etc.). These pins' configuration and logic state is obtained by means of write or read operations in different registers associated with each port.

### You will also find:

- A direction register for an input or output configuration,

- ♣ A data register that copies the logic states of each of the port's pins,

- An option register enabling several input or output configurations.

#### 4.1.2.8. The serial interface

This type of interface allows the microcontroller to communicate with other microprocessor-based systems. The data sent or received takes the form of a succession over time (in a single bit) of binary values that are the image of a word.

There are two types of serial link:

- Synchronous link,

- Asynchronous link.

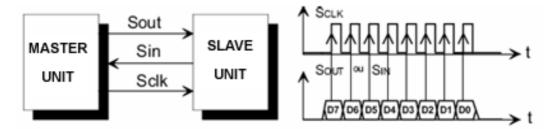

#### Synchronous serial link

In this device transmission is synchronised by a clock signal delivered by the master unit.

Figure 17: Synchronous serial link

#### Asynchronous serial link

This device does not have a synchronisation clock signal. The units that are linked together each have an internal clock set to the same frequency. When one unit wants to transmit a binary word, it generates a falling edge on the transmitter line.

Figure 18: Asynchronous serial link

At the end of transmission of that word, the line switches back to high. The data item to be transmitted may contain an additional bit called the 'parity' bit which is used to correct errors.

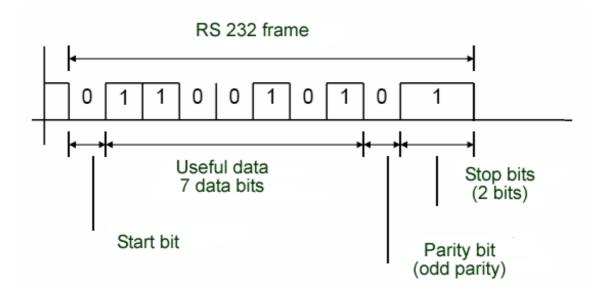

This is the most commonly used type of link in automated systems. *Parameters used for the RS232 standard:*

- Word length: 7 bits (e.g. ASCII character) or 8 bits.

- Transmission speed: this is defined in bits per second or bauds. It can take values going from 110 to 115200 bauds.

- Parity: the transmitted word may or may not be followed by a parity bit which is used to detect any transmission errors that may occur.

- Start bit: at rest the line is at logic state 1 to indicate that a word is going to be transmitted, the line passes to low before starting the transfer. This bit makes it possible to synchronise the receiver clock.

- Stop bit: after transmission, the line is positioned at rest for 1.2 or 1.5 clock periods depending on the number of stop bits.

- ◆ <u>Voltage level:</u> a logic "0" is materialised by a voltage comprised between 3 and 25 V, a logic "1" by a voltage comprised between -25V and -3V.

## 4.1.2.9. The ADC (Analog-to-Digital Converter)

The ADC is generally of the "successive approximations" type. It has several multiplexed inputs, accessible via the pins of the parallel interface ports. The ADC normally has two registers:

- a data register containing the result of the conversion,

- and a control register that is used to run and monitor the conversion.

#### 4.1.2.10. The Timer

The timer is used to perform the following functions:

- Generation of a periodic signal which may or may not be modulated in pulse width,

- Generation of a calibrated pulse,

- Timeout.

- Event counting.

There are several registers associated with the Timer making it possible to configure the various modes described above.

## 4.1.2.11. The Watch Dog

### Don't worry, this isn't a Pit Bull that guards the PLC!!!!

This device is a system that prevents the PLC from crashing. It makes sure that there is no prolonged execution of the same sequence of instructions.

It also checks the correct operation of the hardware and software.

In fact it is a pre-loadable counter that counts down regularly in step with the clock's frequency.

If no pre-loading is performed before it reaches "0" a Reset is generated to restart the PLC.

You must therefore ensure that this watch dog is regularly pre-loaded by a program when it is activated.

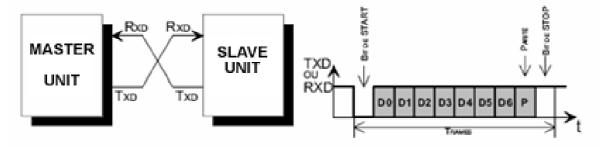

#### 4.1.2.12. The clock signals

The clock signal is used to set the PLC's operating frequency. The PLC includes a Schmitt trigger gate that constitutes an oscillator. To obtain this we place a quartz between the two "OscIn" and "OscOut" pins as shown in the diagram

Figure 19: Clock signals

## 4.1.2.13. The exchange bus

We can see that:

- ♣ The exchanges of information between the different parts of the PLC (inputs, outputs, memories, etc.) always pass through the processor,

- Because operation is sequential, there is never more than one part in communication with the processor at a time,

It is therefore possible to use a common path and a common procedure for the exchanges. This path is called a **BUS**.

The bus consists of address lines, data lines and control lines.

The PLC thus adopts the typical structure of a computer.

#### 4.2. HOW IS THE PROGRAM PROCESSED IN THE PLC?

As you have understood, the way the PLC functions depends on a program that we have assigned to it in the CPU board. In the following chapters, we will look at the *different programming languages*.

In this chapter we are going to focus on the interpretation and management of the program by the PLC.

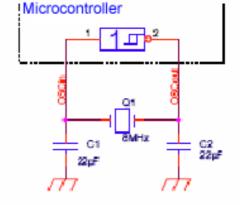

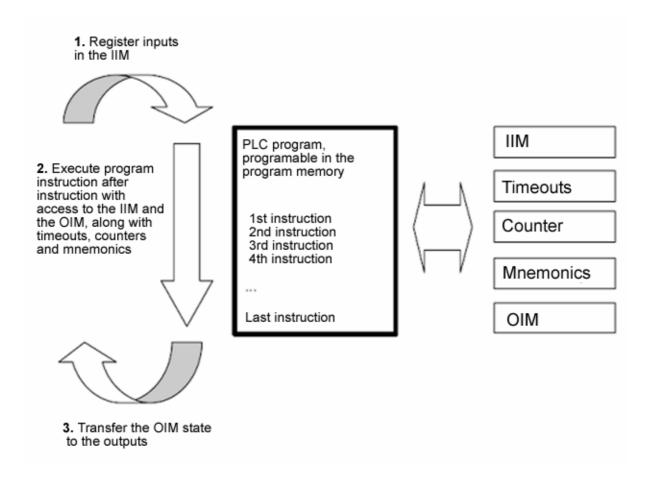

Processing of the program in the PLC is cyclic and takes place as follows:

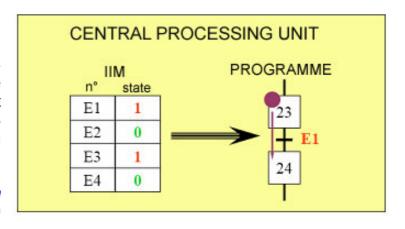

1. After powering up the PLC, the processor which represents the PLC's brain, checks whether each input is powered or not. The state of these inputs is recorded in the input image memory (IIM). If the input is powered, information 1 or "High" will be recorded. If the input is not powered, information 0 or "Low" will be recorded.

#### Example:

The E1 and E2 input LEDs are on, so their logic state is "1":

Figure 20: Example of program processing (1)

In the top image the PLC is in the STOP position.

In the bottom image, the PLC is in the RUN position.

Signal matching and filtering

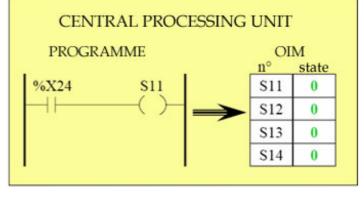

2. This processor runs the program stored in program memory. This consists of a list of instructions and logic operations executed sequentially (various standardised languages can be used). The input information required for this purpose is taken from the input image memory read beforehand and the logic results are written in an output image memory (OIM). During program execution, the processor also accesses the counters, timeouts and mnemonics memory zones (data memory).

#### Example:

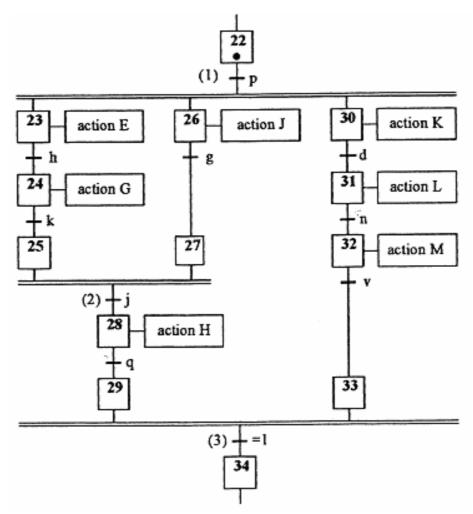

In this example, the PLC program is based on the Sequential Function Chart language (we will see how this functions in detail later on in this course):

Figure 21: Example of program processing (2)

In this example we can see that once inputs E1 and E2 are active, this makes us go from one step to the next (progression from step 23 to step 24) in the program according to input E1 (see Sequential Function Chart chapter).

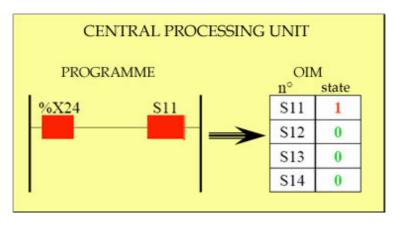

**3.** In the third step, the state is transmitted after execution of the program that uses the OIM on the outputs, activating or deactivating them. Program execution therefore returns to point 1.

#### Example:

Here is the state of the output internal memory when the program has not yet been polled by the PLC:

Figure 22: Example of program processing (3)

Once the PLC has effectively polled the program, we can see that it effectively activates step %X24 which passes to 1 and therefore output S11 effectively changes state in the OIM: the execution order is effectively given.

Figure 23: Example of program processing (4)

From this we can deduce with the help of the diagram below, the general functioning of a program in a PLC:

Figure 24: Schematic diagram of program processing by the PLC

#### Remark:

The time required by the processor to execute the program is called the **cycle time**. The latter depends, among other things, on the number and type of instructions.

#### To summarise:

The PLC reads all the states of the input boards which consist of 0s or 1s: this is the **machine language.**

Once this reading has been completed, the processor processes the program stored in the program memory and then decodes all the information in assembler (language understood by the microprocessor) and can then give its orders on the output boards.

#### 4.3. HOW THE PLC'S INPUT/OUTPUT BOARDS FUNCTION

There are two sorts of I/O signal:

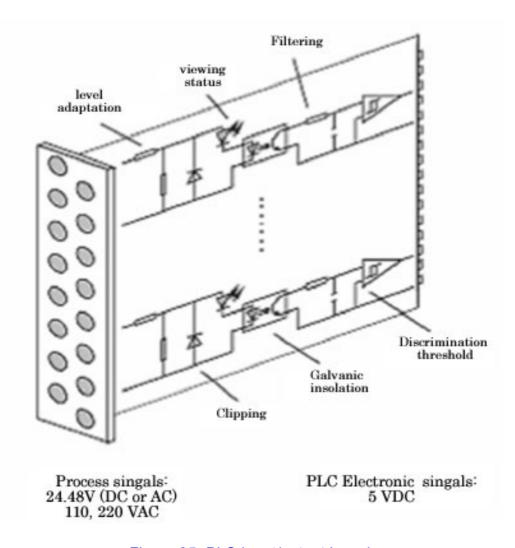

**Digital I/O**: these represent logic signals. Besides acquiring information, binary input devices perform the following operations:

- signal shaping (calibration)

- filtering (elimination of disturbances)

- Isolation (galvanic or by light)

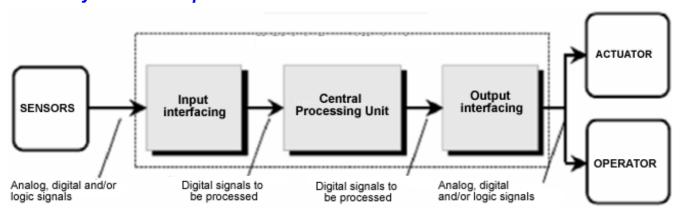

Figure 25: PLC input/output board

The input/output boards therefore create the interface between the signals from the process (to the actuators or from the sensors) and the signals from the PLC's internal bus.

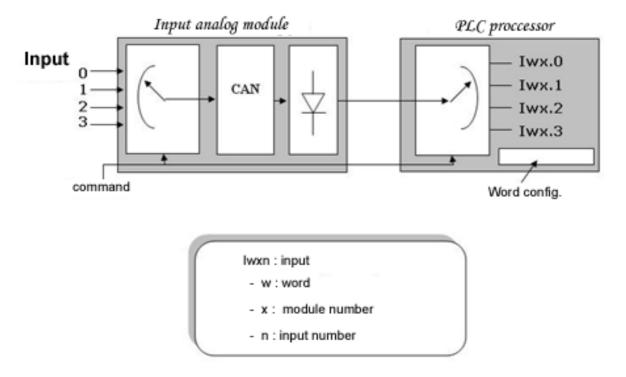

**Analog I/O:** analog inputs transform a continuously varying analog value into a digital code, generally on 11 bits plus one sign bit.

These inputs have a single Analog-to-Digital Converter (ADC), they are polled one after the other by a multiplexer (MUX). Analog outputs, however, only have one converter per channel.

The analog I/Os are characterised by the amplitude of the signal (VH and VL), by the conversion speed and by the electrical value (current or voltage).

At the level of the inputs, there are three types of analog inputs:

- High: 0-10V, 0-20mA, 4-20mA

- For a thermocouple: 0-20mV, 0-50mV, 0-100mV

- For Pt100 probes: 0-100mV, 0-250mV, 0-400mV

Likewise, the analog inputs can be differentiated according to these intervals:

0-10V, 0-5V, ±10V, ±5V, 0-20mA, 4-20mA.

Figure 26: Conversion of analog signals

This module has four channels and a single Analog-to-Digital Converter.

Each channel is processed by means of the associated multiplexer.

The conversion time per channel depends on the converter and therefore on the PLC.

In the case of the TSX 17-20 PLC, this time is 15ms; so the total conversion time is: 4 \* 15 = 60ms.

To correctly assess the performance of a PLC on the basis of its critical speed, you will have to calculate its effective conversion time as follows:

$$T_{conv.effect} = T_{cycle} x (1 + integer part (T_{conv.total} / T_{cycle}))$$

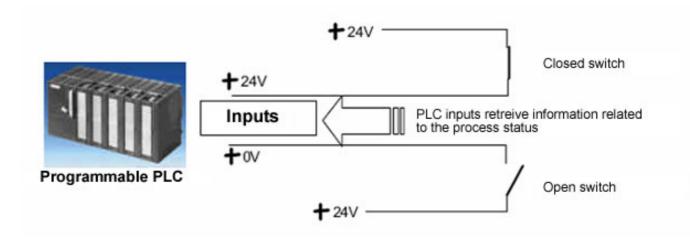

## 4.3.1. Logic inputs operation

The PLC receives the information on the process via the signal sensors connected to the PLC's inputs.

These signal sensors may, for example, be sensors that will recognise whether a part being machined is in a given position, or simple switches that can be closed or open.

A distinction must also be made between normally closed contacts that are closed at rest and normally open contacts that are open at rest.

Figure 27: Logic input operation

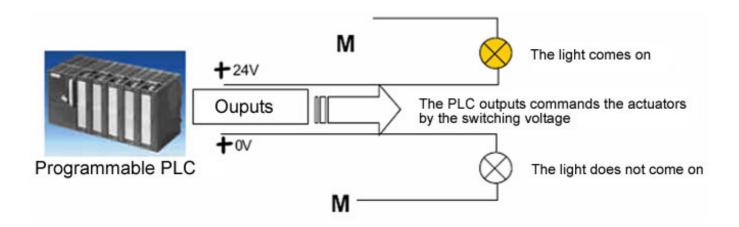

### 4.3.2. Logic outputs operation

The PLC commands the process by applying a voltage of 24V, for example, to the actuators via the PLC's connection points called *outputs*. This makes it possible to activate or deactivate motors, to make solenoid valves rise or fall or to switch lights on or off.

Figure 28: Logic output operation

# 4.3.3. Passive or active input / output board?

A distinction must be made between an active or passive board.

### What does this actually mean?

In the case where your PLC has active input/output boards, it is the PLC itself that delivers the power supply (24VDC, 48VDC, 110VAC, etc.).

In the case where your PLC has passive input/output boards, you will imperatively have to power each of your inputs/outputs by means of an external power supply.

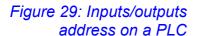

## 4.3.4. How does the PLC address the input/output signals?

The declaration of an input or output within a program is called **addressing**.

The inputs to and outputs from PLCs are usually grouped together in sets of eight digital inputs or outputs.

This set of eight inputs or outputs is called a **byte**. Each group receives a number called the **byte address**.

In order to enable the addressing of an input or output inside a byte, each byte is divided into eight bits.

The latter are numbered 0 to 7. We thus obtain the **bit's** address.

The PLC represented below has input bytes 0 and 1, and output bytes 4 and 5.

The inputs/outputs addressing is written by default in the PLC and we will see in the software part of this course how each input/output should be filled in correctly with our own comments, this operation is carried out in the CPU board's **mnemonics table**.

### Example 1:

To address the fifth input from the top, you must enter the following address:

10.4

I indicates the type of address (in this case the 'I' means Input: it is an input) 0 indicates the byte's address

4 is the bit's address (this is simply your board's channel number)

The byte's address and the bit's address are always separated by a dot.

You are probably saying to yourself: "I don't understand, we wanted the fifth input and we have written 4 for the bit's address": this is normal because numbering starts at 0.

### Example 2:

To address the last output, you must enter the following address:

05.7

O indicates the type of address (in this case the 'O' means Output: it is an output) 5 indicates the byte's address 7 is the bit's address

## 5. THE SOFTWARE PART

### 5.1. INTRODUCTION

## 5.1.1. History of programming languages

Like for any computer, the program is constructed using a language. This language is a set of instructions that apply to variables. Due to the specific function of industrial machine and process control, a history, not to say a culture has developed around specific languages.

On the one hand, computer languages of course. These languages have been developed according to two tendencies: the PLC's application and processor. Must they meet the needs of mathematicians, software specialists or manufacturers of electronic microcircuits?

It must not be forgotten that, in the end, it is a machine code that will be executed.

On the other hand, the automation practitioners: electrical, mechanical, instrumentation technicians? Here, we can distinguish between two main cultural families due to their history.

In North America, through the specialisation of tasks, it would seem that it is the electricians who have the monopoly of the language. Based on drawings and control diagrams, it is the ladder diagrams language that has been generalised.

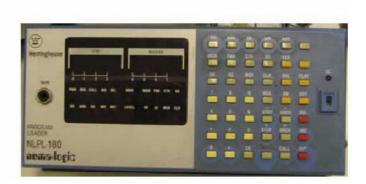

Figure 30: Examples of programming consoles

It is true that there have been some attempts by "IT specialists" to impose a so-called mnemonics language, but it wasn't popular with the electricians and instrumentation specialists. It is however the language closest to the assembler that the PLC's processor uses.

Training Manual EXP-MN-SI090-EN Last revised on: 17/12/2008

We used to use small, simple programming consoles that make it possible to see and/or enter the instructions one by one. These consoles can still be used from time to time for simple modifications.

In short, it is the **ladder** that had won, so now it was left to the IT specialists to develop editors (that draw symbols: contacts and windings on a screen), and compilers (that transform those symbols into instructions... mnemonics that the PLC can execute) so that the electricians and instrumentation specialists can find their way.

These PLC programming software applications were either dedicated microcomputers (figure below) or software applications installed on a PC (such as PL7 pro, STEP 7, etc.).

Figure 31: Examples of microcomputers dedicated to programming

In the rest of the world, the specialisation of the automation experts is not so clearly cut. Or at least it was becoming a specialisation in its own right. Furthermore, a technology came between the relay and the PLC: static logic.

Based on the concept of wired gate logic, it uses the symbols of gates but with a technology suited to the reality of the industrial world: 24VDC voltage, shielding and decoupling.... All the suppliers have invested in this, with greater or lesser success.

Square D developed its Norpack (nothing but NOR gates), Allen Bradley, Westinghouse, Siemens (Siematic), Télémécanique (Téléstatic) and Merlin Gérin with its Silimog.

Just as the relay logic gave ladder language, gate logic has given the function block language. We found the same programming software applications: a symbols (the blocks) editor and a compiler to transform the symbols into instructions that can be run by the PLC.

All these languages were, in the end, poorly suited to describing complex operations that often include sequences. They were made for combinatorial logic; even if sequential instructions had been developed such as the cyclic programmer (Drum), but this was very limited.

Training Manual EXP-MN-SI090-EN Last revised on: 17/12/2008

A solution was found by the mechanics because they found that it was difficult to describe the operation of a machine or of a process using words (and syntax).

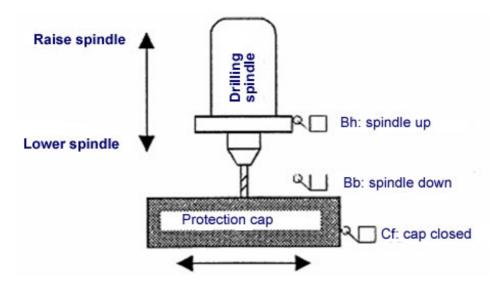

This gave something like this:

Put the part in the vice, tighten, when it has been tightened start the drill's motor, lower the drill quickly to the edge of the part, then lower slowly, raise the drill to clear if the hole is deep, and drilled to the correct depth. Raise the drill, and once it has been fully raised, loosen the part and remove it...

All you needed to know then was how you put the part in the vice, how you tightened it, when did you know it had been tightened, how do you start the motor, how do you lower the drill quickly, not so quickly.... How do you know you are close to the part? That the hole is deep? That you have drilled to the right depth.... And what happens if the motor doesn't work, if the drill bit breaks?

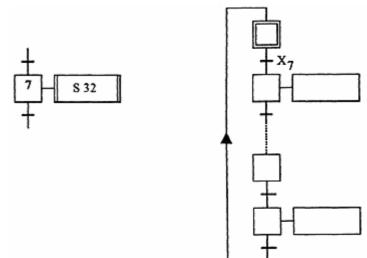

Towards the end of the seventies, the AFCET committee examined the question of how to describe an automatic system and created a language for describing an automatic system: the **Sequential Function Chart** was born.

It was standardised under the reference CEI60848 in 1988 and revised in 2002.

It was only much later on that Sequential Function Chart became a programming language for PLCs. However, as the description language existed, it just had to be translated into a control language.

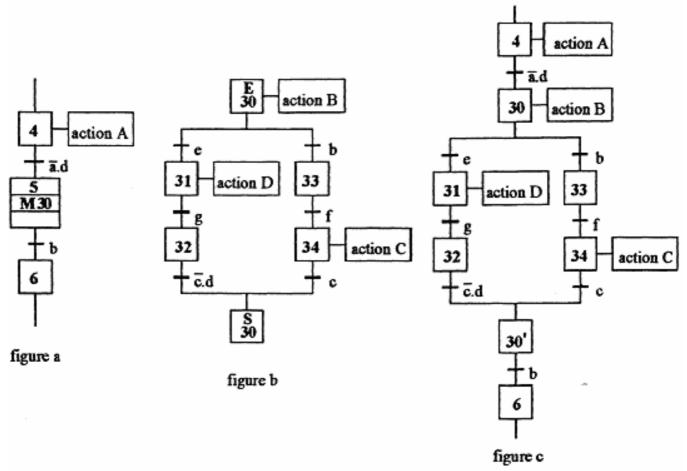

This period of Sequential Function Chart-ladder coexistence seems to be lasting, to such an extent that we now find automatic translation software applications that use the ladder instruction sets of PLCs.

Here we must make an important remark: Sequential Function Chart as a programming language (therefore more than a description language) has had significant implications on the operating principle of PLCs. The cycle that we use for conventional logic is modified quite significantly and is simplified when you use the **Sequential Function Chart language** in a PLC.

When the PLC arrives at the Sequential Function Chart section, it only looks at the validated transitions: the transitions for which all the immediately preceding steps are active. If a step must be passed because the transition is true, it activates the immediately following steps and deactivates all the previous steps.

To conclude this introduction, in the face of the challenges of globalisation, it is necessary that a machine or process designed in Italy, for example, should function in Japan: this required standardisation.

### 5.1.2. The IEC 61131-3 standard

This is what the IEC did starting in 1993, in cooperation with the PLCopen organisation which together took an active part in writing the IEC61131 standard.

This standard defines the program design procedures for ensuring transportability: achieve independence from the specific features of a given type of hardware (PLC brand and model).

This ever-evolving standard defines how to implement programs on the basis of this standard. It makes the distinction between the common elements and **two families of languages**: **textual languages** and **graphic languages**.

### The textual languages are:

- ♣ The Instruction List (IL), this is a mnemonic language used in part by the IT specialists,

- The Structured Text Language (ST), which is used very little these days.

### The graphic languages are:

- ♣ The Ladder Diagram (LD),

- ♣ The Sequential Function Chart (SFC),

- ♣ The Function Block Diagram (FDB)

## 5.2. LADDER LANGUAGE (LD)

#### 5.2.1. Introduction

The ladder diagram (LD) is a graphic programming language. This is a visual language that is very easy to use and whose graphic representation is close to that of electrical diagrams. Associated with the Function Block Diagram (FBD) the ladder becomes a complete programming language.

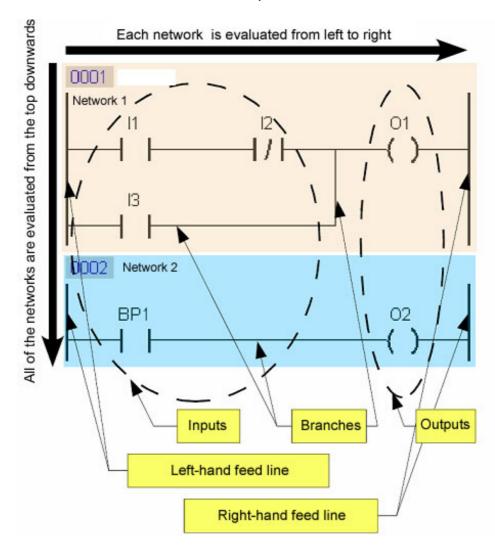

A Ladder Diagram is made up of several networks. As you can see in the figure below, each network has a left-hand feed line, a right-hand feed line and branches connecting the inputs on the left to the outputs on the right.

Each network is evaluated from left to right.

All of the networks are evaluated from the top downwards.

Figure 32: Ladder Diagram operating principle

We make a distinction between the instructions on bits and the instructions on words. We also make a distinction between the test instructions and the write or assign instructions.

### Example:

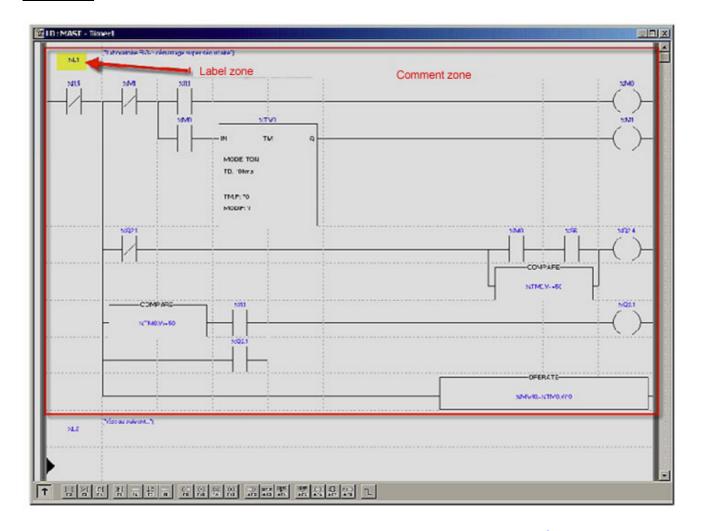

Figure 33: Ladder contact diagram in Télémécanique's PL7 software:

A network is a zone comprised between two tables (labels). In the figure above you can see network %L1 and part of network %L2. Each network may have comments. A label must be unique in a program.

The graphic zone is situated below the label and comment zones. It is divided into cells.

There are 11 columns of cells and you can have up to a maximum of 16 rows in a network. The elements can occupy one or more cells.

### 5.2.2. Instructions on bits

## 5.2.2.1. The tests (contacts)

- The contact closes when the bit is at 1

- In the contact closes when the bit is at 0

- P Rising edge: the contact closes during 1 scan when the bit passes from 0 to 1

- N Falling edge: the contact closes during 1 scan when the bit passes from 1 to 0

The AND (in series) and OR (in parallel) logic operations are realised by graphic connection symbols.

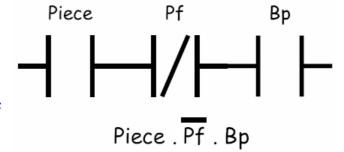

### 5.2.2.2. Series contacts

By associating contacts in series you can make logic ANDs.

Figure 34: Example of series contacts

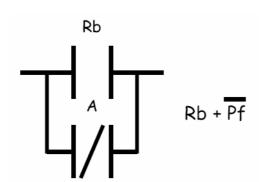

### 5.2.2.3. Parallel contacts

By associating contacts in parallel you can make logic ORs.

Figure 35 : Example of parallel contacts

## **5.2.2.4.** Writing (coils)

- The coil is activated, the bit passes to 1 as long as the preceding logic is at 1 and the coil is deactivated, the bit passes to 0 if the logic is at 0.

- The coil is activated, the bit passes to 1 as long as the preceding logic is at 0 and the coil is deactivated, the bit passes to 0 if the logic is at 1.

- -(S)- The coil is activated, the bit passes to 1 as long as the preceding logic is at 1 and remains like that even if the logic returns to 0.

- -(R)- The coil is deactivated, the bit passes to 0 if the preceding logic is at 1 and remains like that even if the logic returns to 0.

- -(#)- Instruction reserved for a reception from the Sequential Function Chart. If the associated transition is validated, the transition is made.

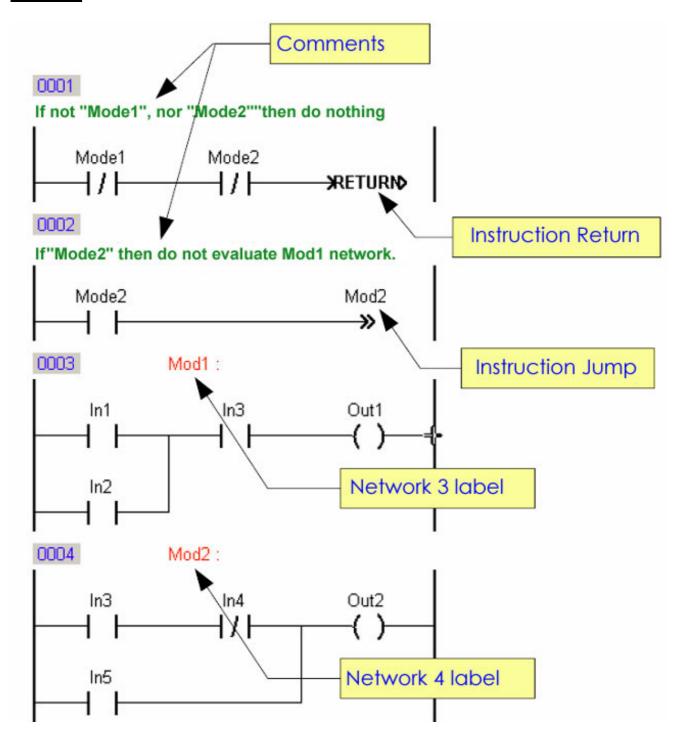

## 5.2.2.5. Network jumps and comments

## **Jump**

The "Jump Label" conditional instruction makes it possible to skip, that is to say exclude, the evaluation of all the networks placed between the "Jump Label" and the network "Label"»

#### RETURN

The "Return" conditional instruction makes it possible to skip, that is to say exclude, the evaluation of all the networks placed after the "Return"

#### **Comments**

It is possible to insert comments at the beginning of each network.

## Example:

Figure 36: Example of jumps and comments

### 5.2.3. Instruction on words

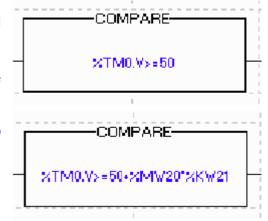

## 5.2.3.1. The tests (comparisons)

There are two types of comparison:

## ♣ The horizontal comparison (the most frequently used)

The two variables are separated by numerical test signs: =, <, >, =<, =>, <> (different).

The second variable may be a numerical value or an operation.

Figure 37: Horizontal comparison

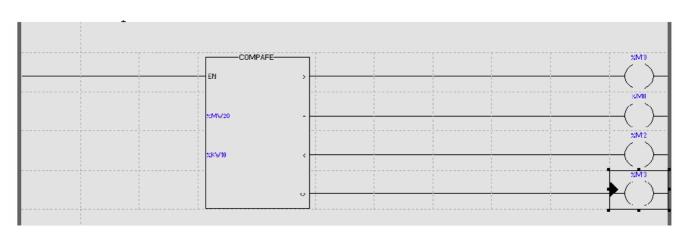

## The vertical comparison:

The four possibilities can be used and combined.

For example, %M10 or %M11 will be true if %M10 is greater than or equal to %KW10.

Figure 38: Vertical comparison

## 5.2.3.2. The assignments (OPERATE)

Simply put, this makes it possible to transfer a value in a variable.

Figure 39: Assignments (OPERATE)

Training Manual EXP-MN-SI090-EN Last revised on: 17/12/2008

In the example above, %MW10 will be equal to %TM0.V divided by 10.

This also makes it possible to perform more complex calculations and functions: conversions, indexation, communication.

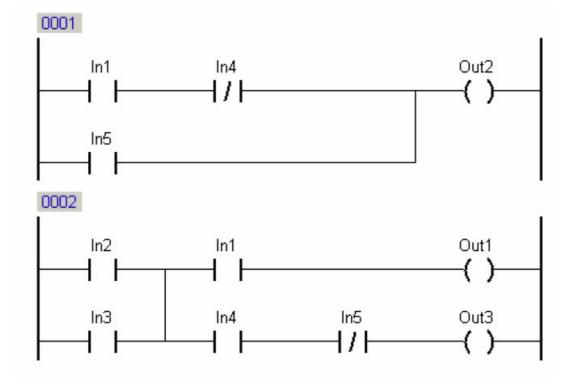

### 5.2.3.3. The combinatorial functions

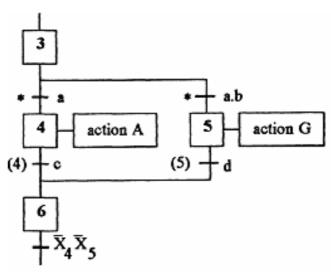

We are going to program the following logic equations in ladder language:

Out1 =

$$ln1 \cdot (ln2 + ln3)$$

Out2 =

$$\ln 1 \cdot I_{n4} + \ln 5$$

Out3 =

$$\overline{In5} \cdot \ln 4 \cdot (\ln 2 + \ln 3)$$

Here is the program in Ladder Language for our logic equations:

Figure 40: Logic equations in ladder language

## 5.2.3.4. The bistable and pulse functions

The Manual – Off – Automatic 3-position selector switch delivers 2 items of Boolean information according to the truth table below:

| -         | Manual | Off | Automatic |

|-----------|--------|-----|-----------|

| Manual    | 1      | 0   | 0         |

| Automatic | 0      | 0   | 1         |

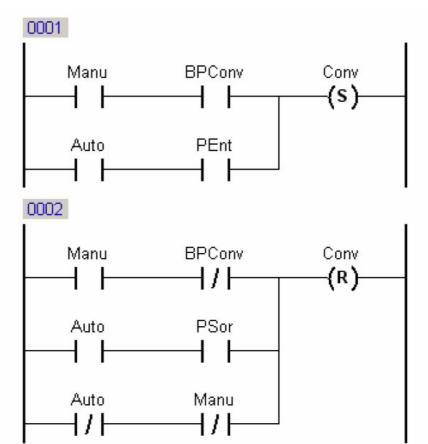

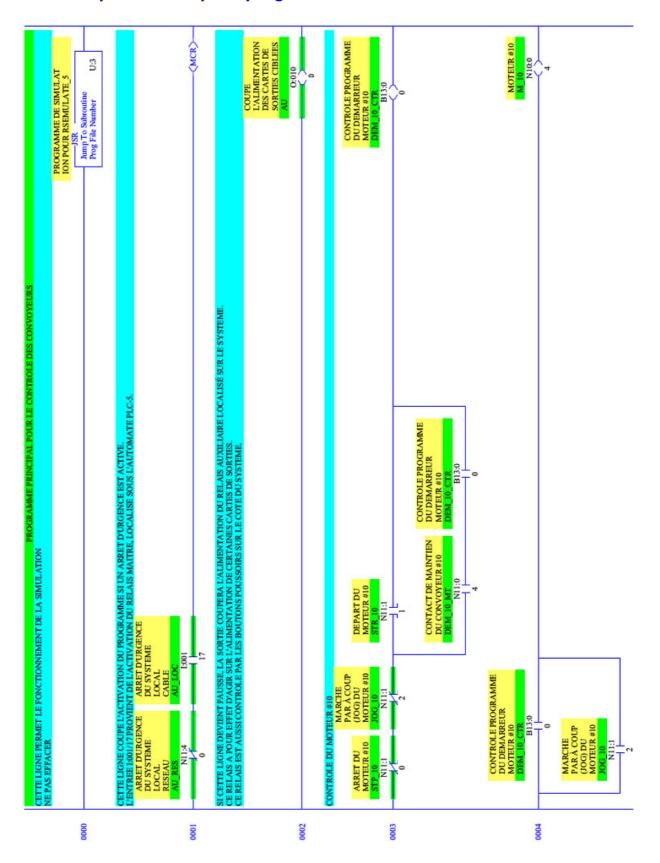

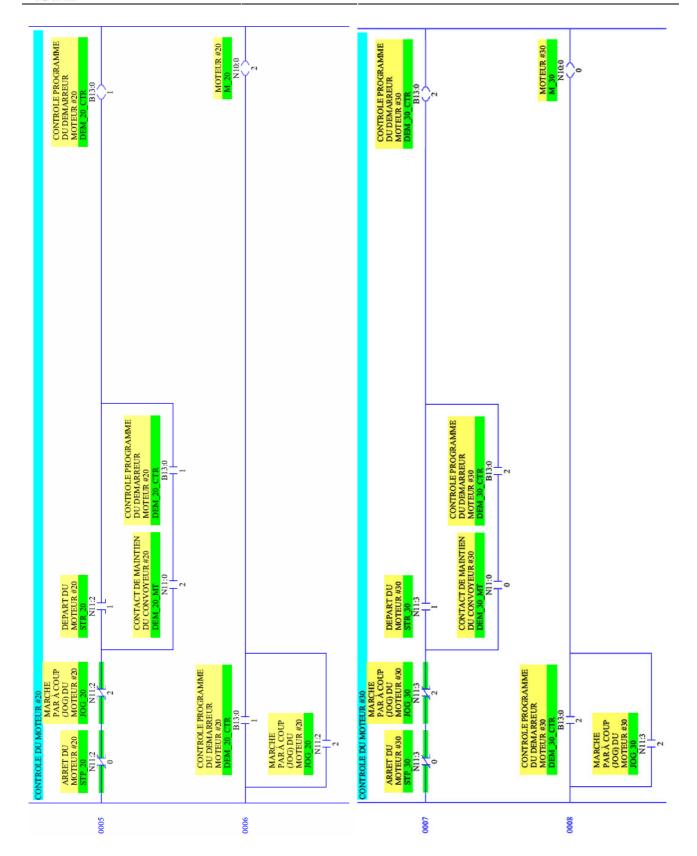

## Let's take a small example:

If the selector is in the Manual position then the conveyor belt, Conv output, functions if the BPConv input is at 1.

If the selector is in the Automatic position, then a rising edge on the PEnt input starts up the conveyor belt and a falling edge on the PSor outputs stops the conveyor belt.

We are now going to write a brief expression of requirements:

Figure 41: Example of selector switch programming

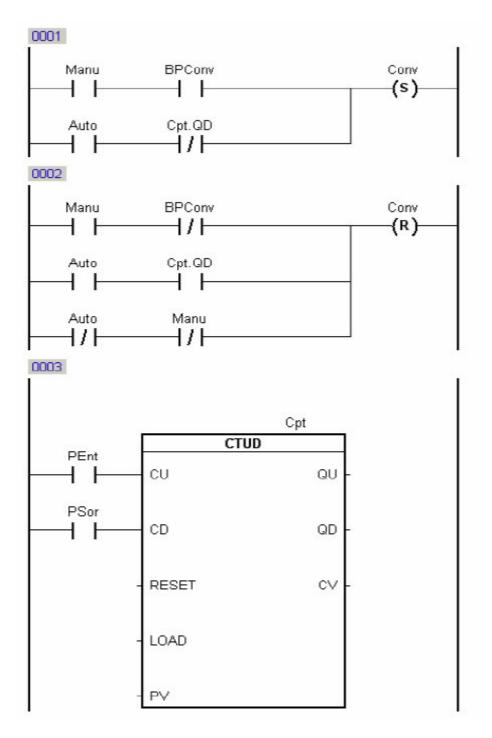

# Using function blocks in FBD language

We are going to take the same example as above and combine the ladder with the FBD, and this gives:

Figure 42: Using Function Blocks in FBD language

# 5.2.4. Example of a complete program

## 5.3. FUNCTION BLOCK DIAGRAM (FBD) LANGUAGE

All the functions and all the function blocks in the various libraries can be inserted in the ladder networks.

The functions and function blocks are program organisation units common to all the programming languages.

### 5.3.1. The Functions

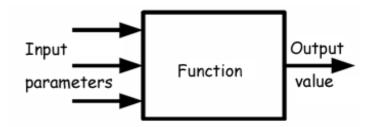

A function is a program organisation unit which, when it is executed, provides exactly a data element (value, structure, table, etc.). It is an operand in an expression.

A function does not contain any information concerning its internal state, that is to say the triggering of a function with the same input parameters always gives the same output value.

Figure 43: Functions

### 5.3.2. The standard functions

### 5.3.2.1. The conversion functions

The conversion functions make it possible to change a value's type. For example the BOOL\_TO\_INT function transforms a Boolean value into a 16-bit integer value.

### 5.3.2.2. The numerical functions

| Function | Symbol | I/O type | Description                       |  |

|----------|--------|----------|-----------------------------------|--|

| ABS      |        | ANY_NUM  | Absolute value                    |  |

| SQRT     |        | ANY_REAL | Square root                       |  |

| LN       |        | ANY_REAL | Neperian logarithm                |  |

| LOG      |        | ANY_REAL | NY_REAL Decimal logarithm         |  |

| EXP      |        | ANY_REAL | Exponential                       |  |

| SIN      |        | ANY_REAL | Sine (angle expressed in radians) |  |

Training Manual EXP-MN-SI090-EN Last revised on: 17/12/2008

| Function | Symbol | I/O type                    | Description                               |

|----------|--------|-----------------------------|-------------------------------------------|

| cos      |        | ANY_REAL                    | Cosine (angle expressed in radians)       |

| TAN      |        | ANY_REAL                    | Tangent (angle expressed in radians)      |

| ASIN     |        | ANY_REAL                    | Principal arc sine (result in radians)    |

| ACOS     |        | ANY_REAL                    | Principal arc cosine (result in radians)  |

| ATAN     |        | ANY_REAL                    | Principal arc tangent (result in radians) |

| ADD      | +      | ANY                         | Addition                                  |

| SUB      | -      | ANY                         | Subtraction                               |

| MUL      | *      | ANY_NUM                     | Multiplication                            |

| DIV      | /      | ANY_NUM                     | Division                                  |

| MOD      |        | ANY_INT                     | Remainder of the integer division         |

| EXPT     | **     | ANY_REAL <sup>ANY_NUM</sup> | Power (IN1 <sup>IN2</sup> )               |

| MOVE     | ;=     | ANY                         | Assignment                                |

Figure 44: The numerical functions in FBD language

## 5.3.2.3. The selection and limitation functions

| Function                          | I/O type | Description                 |  |

|-----------------------------------|----------|-----------------------------|--|

| SHL                               | ANY_INT  | N-bit shift to the left     |  |

| SHR                               | ANY_INT  | N-bit shift to the right    |  |

| ROL                               | ANY_INT  | N-bit rotation to the left  |  |

| ROR                               | ANY_INT  | N-bit rotation to the right |  |

| AND                               | BOOL     | AND logic operator          |  |

| OR                                | BOOL     | OR logic operator           |  |

| NOT                               | BOOL     | NOT logic operator          |  |

| XOR BOOL Exclusive OR logic opera |          | Exclusive OR logic operator |  |

Figure 45: The selection and limitation functions in FBD language

# 5.3.2.4. The comparison functions

| Function | Symbol          | I/O type   | Description               |

|----------|-----------------|------------|---------------------------|

| GT       | >               | ANY - BOOL | Strictly greater than     |

| GE       | >=              | ANY – BOOL | Greater than or equal to  |

| EQ       | =               | ANY – BOOL | Equal to                  |

| LT       | <               | ANY – BOOL | Strictly lower than       |

| LE       | <=              | ANY – BOOL | Lower than or equal to    |

| NE       | <b>&lt;&gt;</b> | ANY - BOOL | Not equal to or Different |

Figure 46: The comparison functions in FBD language

# 5.3.2.5. The functions on character strings

| Function                  | I/O type             | Description                                                                                   |

|---------------------------|----------------------|-----------------------------------------------------------------------------------------------|

| LEN                       | ANY_STRING - ANY_INT | Returns the length of the character string                                                    |

| LEFT                      | ANY_STRING - ANY_INT | Returns the character string made up of the first N characters                                |

| RIGHT                     | ANY_STRING - ANY_INT | Returns the character string made up of the last N characters                                 |

| MID                       | ANY_STRING – ANY_INT | Returns the character string from the N <sup>th</sup> and until the P <sup>th</sup> character |

| CONCAT                    | ANY_STRING           | Returns the concatenation of the character strings                                            |

| INSERT                    | ANY_STRING - ANY_INT | Inserts a character string from the N <sup>th</sup> character                                 |

| DELETE                    | ANY_STRING - ANY_INT | Deletes N characters from the P <sup>th</sup> character                                       |

| REPLACE                   | ANY_STRING - ANY_INT | Replaces N characters from the P <sup>th</sup> character                                      |

| FIND ANY_STRING – ANY_INT |                      | Returns the first position of a character string in another character string                  |

Figure 47: The functions on character strings in FBD language

# 5.3.2.6. The date and time functions

| Function        | Symb. | IN1           | IN2           | OUT           |

|-----------------|-------|---------------|---------------|---------------|

| ADD             | +     | TIME          | TIME          | TIME          |

| ADD             | +     | TIME_OF_DAY   | TIME          | TIME_OF_DAY   |

| ADD             | +     | DATE_AND_TIME | TIME          | DATE_AND_TIME |

| ADD_TIME        | +     | TIME          | TIME          | TIME          |

| ADD_TOD_TIME    | +     | TIME_OF_DAY   | TIME          | TIME_OF_DAY   |

| ADD_DT_TIME     | +     | DATE_AND_TIME | TIME          | DATE_AND_TIME |

| SUB             | -     | TIME          | TIME          | TIME          |

| SUB             | -     | TIME_OF_DAY   | TIME          | TIME_OF_DAY   |

| SUB             | -     | TIME_OF_DAY   | TIME_OF_DAY   | TIME          |

| SUB             | -     | DATE_AND_TIME | TIME          | DATE_AND_TIME |

| SUB             | -     | DATE_AND_TIME | DATE_AND_TIME | TIME          |

| SUB             | -     | DATE          | DATE          | TIME          |

| SUB_TIME        | -     | TIME          | TIME          | TIME          |

| SUB_TOD_TIME    | -     | TIME_OF_DAY   | TIME          | TIME_OF_DAY   |

| SUB_TOD_TOD     | -     | TIME_OF_DAY   | TIME_OF_DAY   | TIME          |

| SUB_DT_TIME     | -     | DATE_AND_TIME | TIME          | DATE_AND_TIME |

| SUB_DT_DT       | -     | DATE_AND_TIME | DATE_AND_TIME | TIME          |

| SUB_DATE_DATE   | -     | DATE          | DATE          | TIME          |

| MUL             | *     | TIME          | ANY_NUM       | TIME          |

| MULTIME         | *     | TIME          | ANY_NUM       | TIME          |

| DIV             | 1     | TIME          | ANY_NUM       | TIME          |

| DIVTIME         | 1     | TIME          | ANY_NUM       | TIME          |

| CONCAT_DATE_TOD |       | DATE          | TIME_OF_DAY   | DATE_AND_TIME |

Figure 48 : The date and time functions in FBD language

### 5.3.3. The function blocks

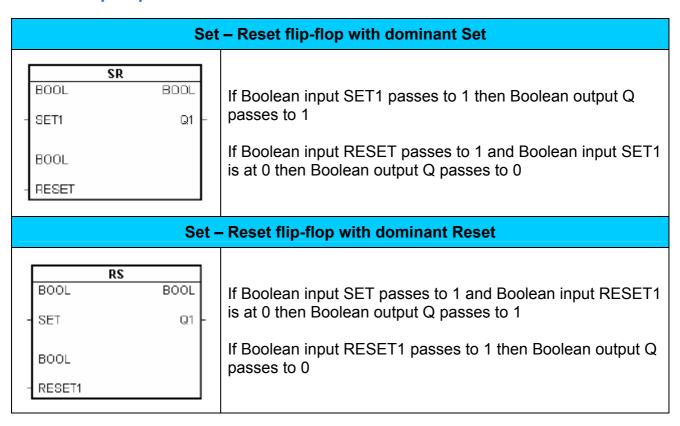

## 5.3.3.1. Flip-flops

Figure 49: The flip-flop function blocks in FBD language

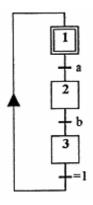

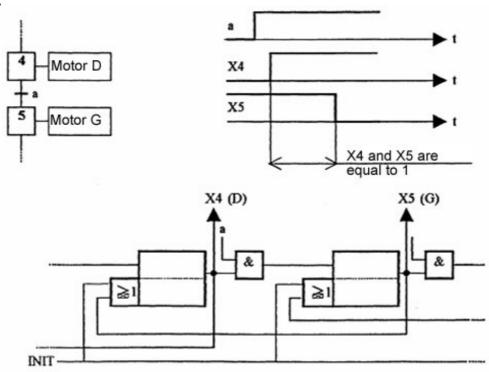

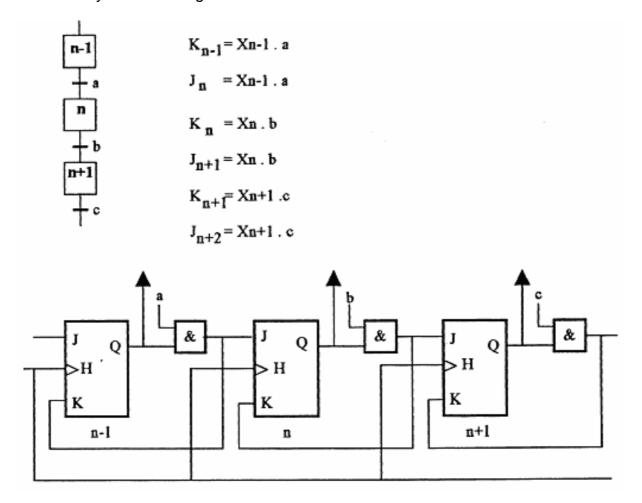

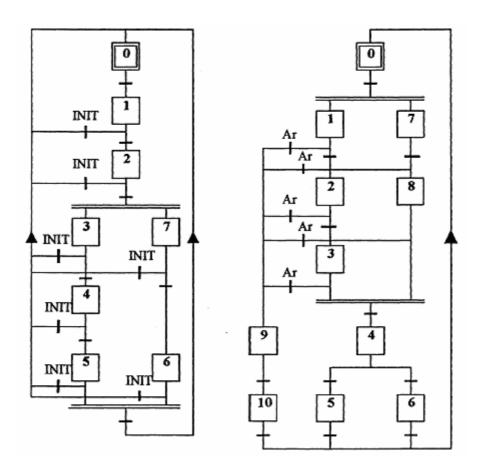

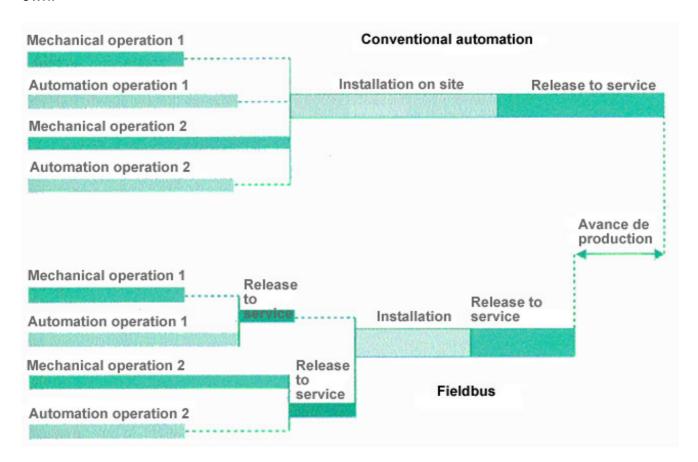

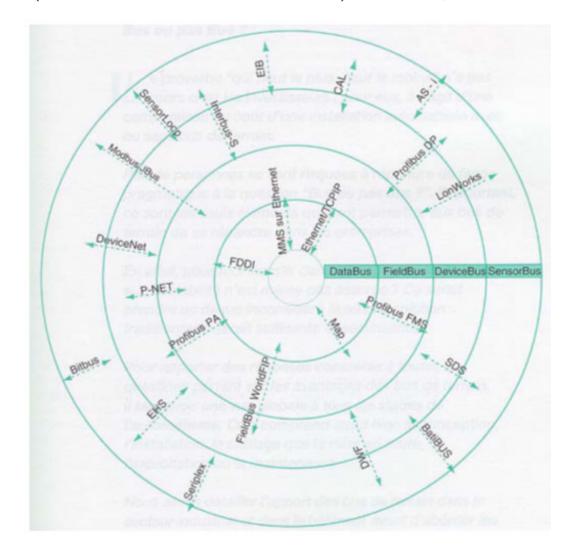

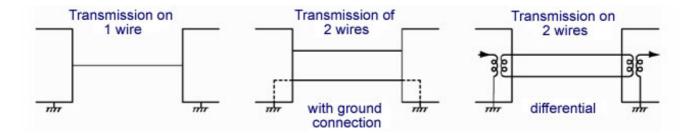

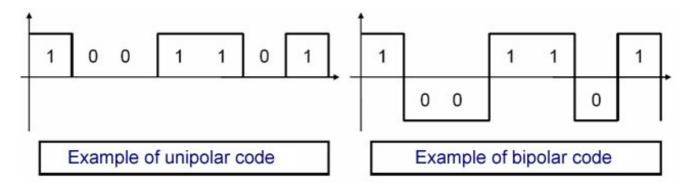

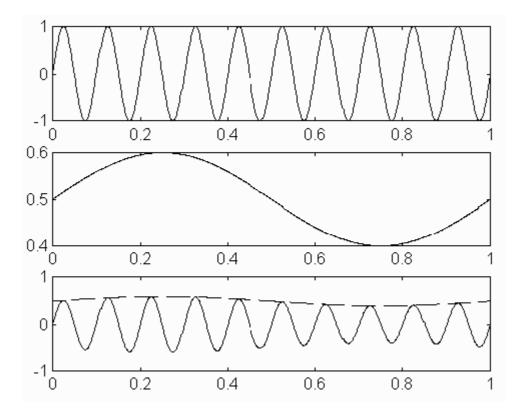

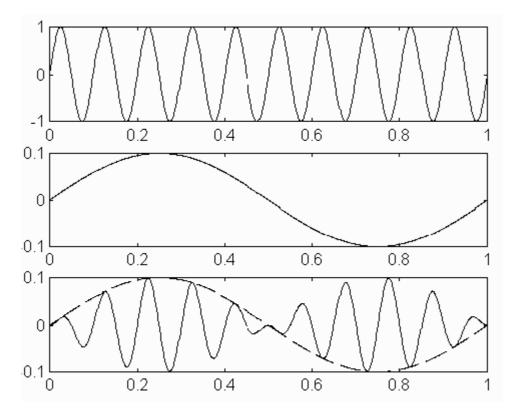

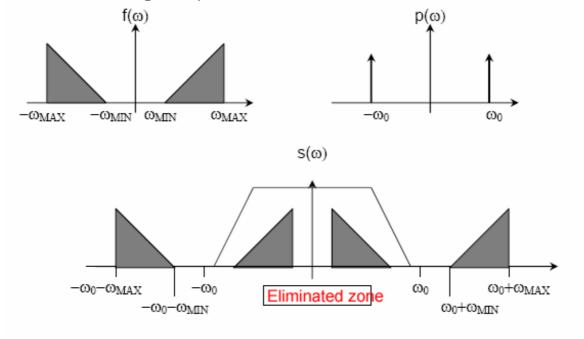

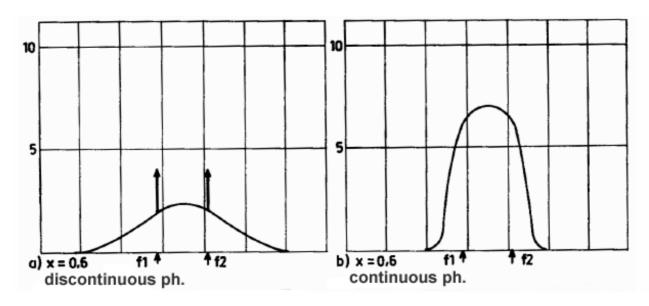

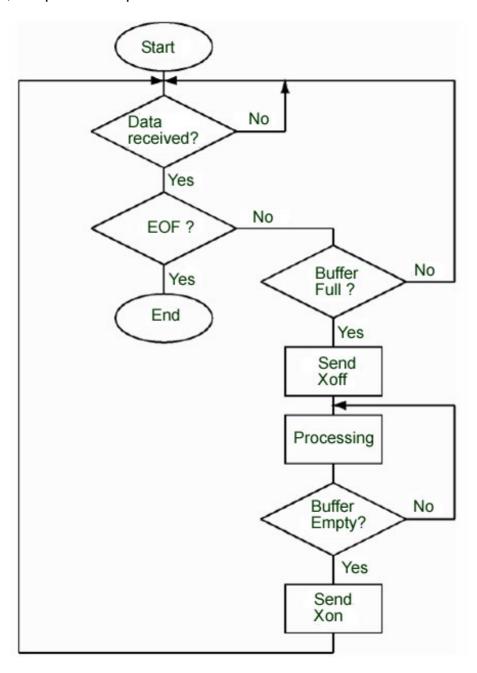

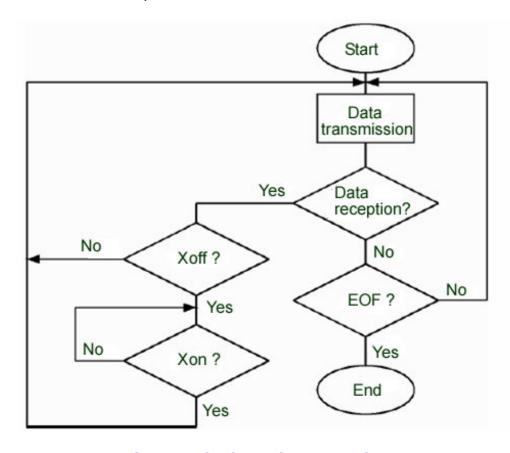

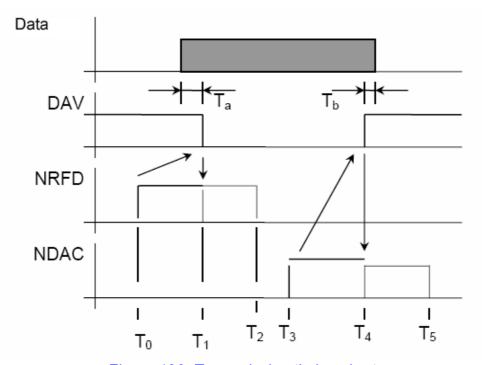

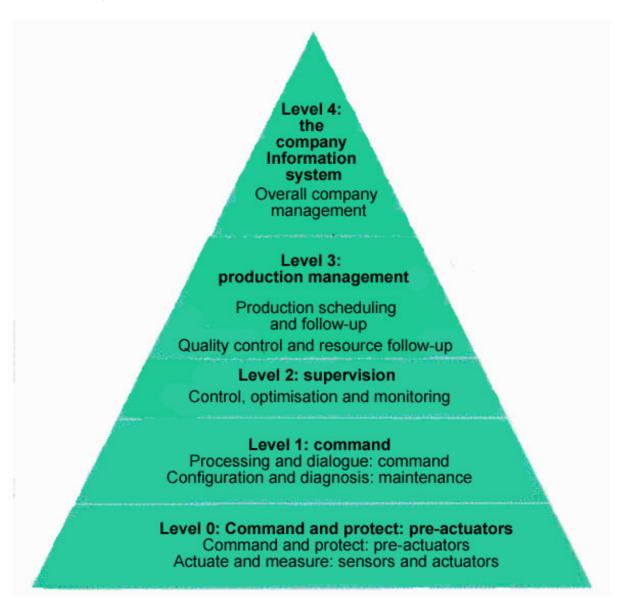

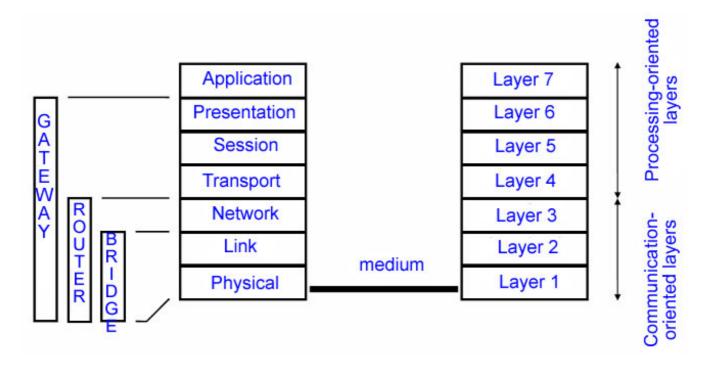

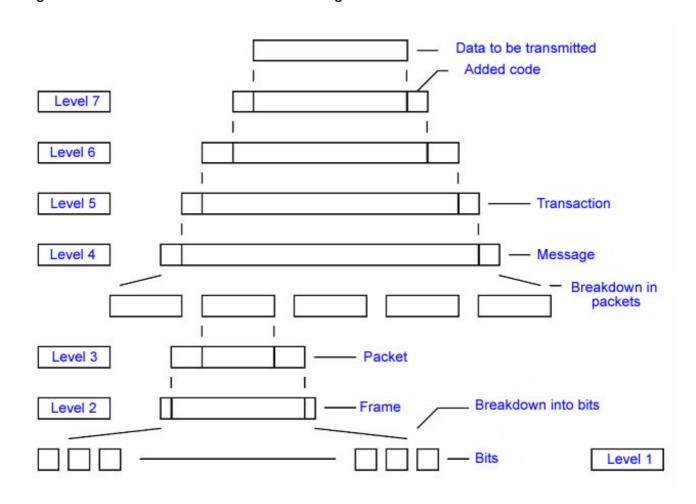

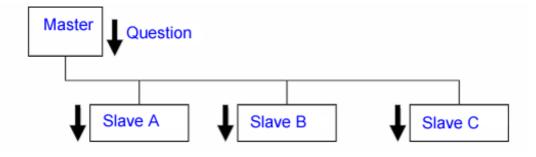

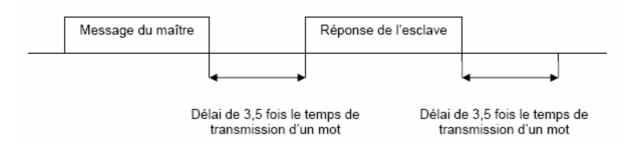

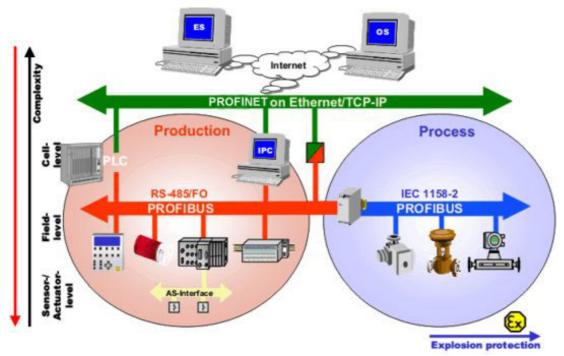

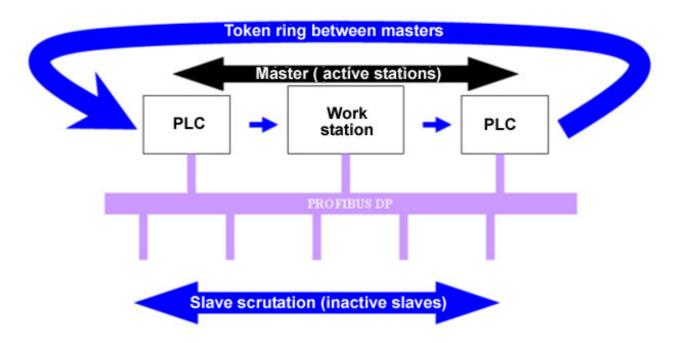

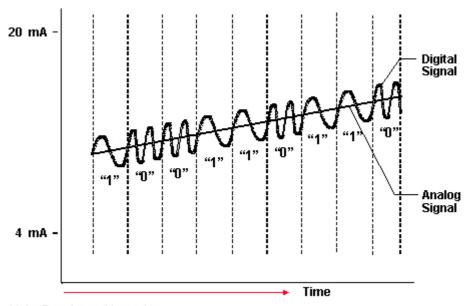

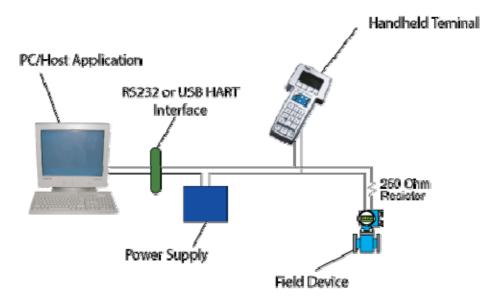

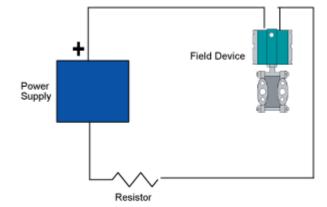

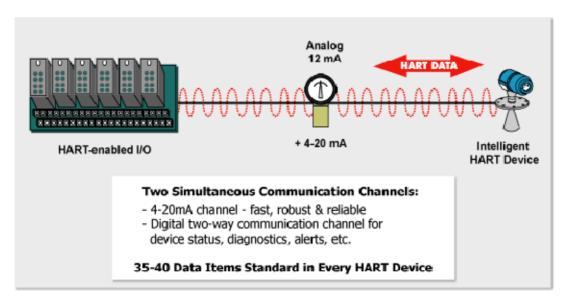

## 5.3.3.2. Edge detection