### Chapter 5

#### **Basics of PLC Programming**

## Processor Memory Organization

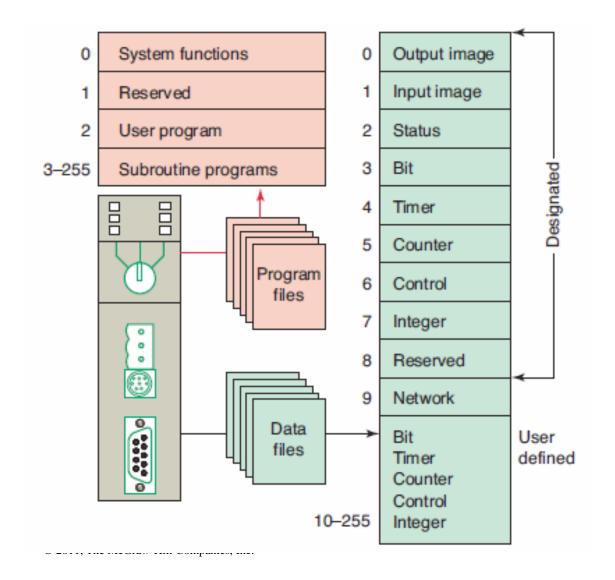

The memory structure for a PLC processor consists of several areas, some of these having specific roles.

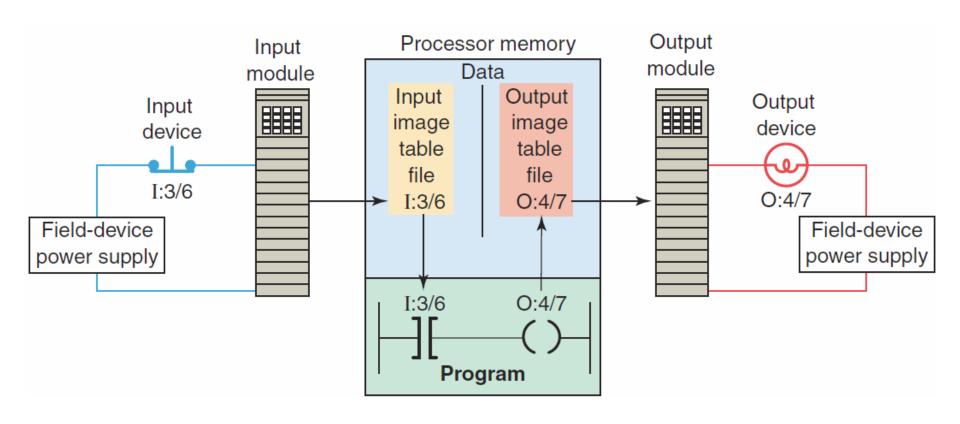

With rack-based memory structures addresses are derived using the rack number, the I/O module slot number and the screw terminal number where the I/O device is wired.

With tag-based memory structures all data are assigned a variable name called a tag. A program can be developed using only tag names but you must assign input and output terminals to input and output tags before the program can be executed

### The memory space can be divided into two broad categories: *program files* and *Data files*.

Program and Data file organization for the SLC 500 controller.

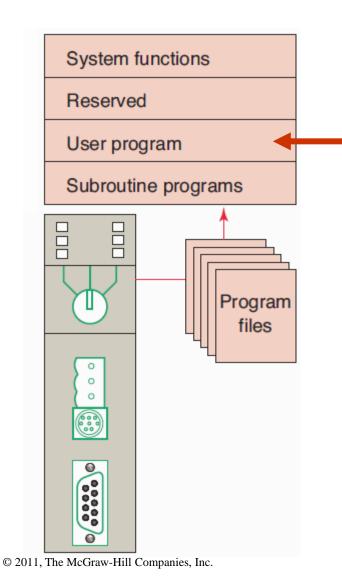

## **Program files** are the areas of processor memory where ladder logic programming is stored.

Program files are the part of the processor memory that stores the user ladder logic program. The program accounts for most of the total memory of a given PLC system.

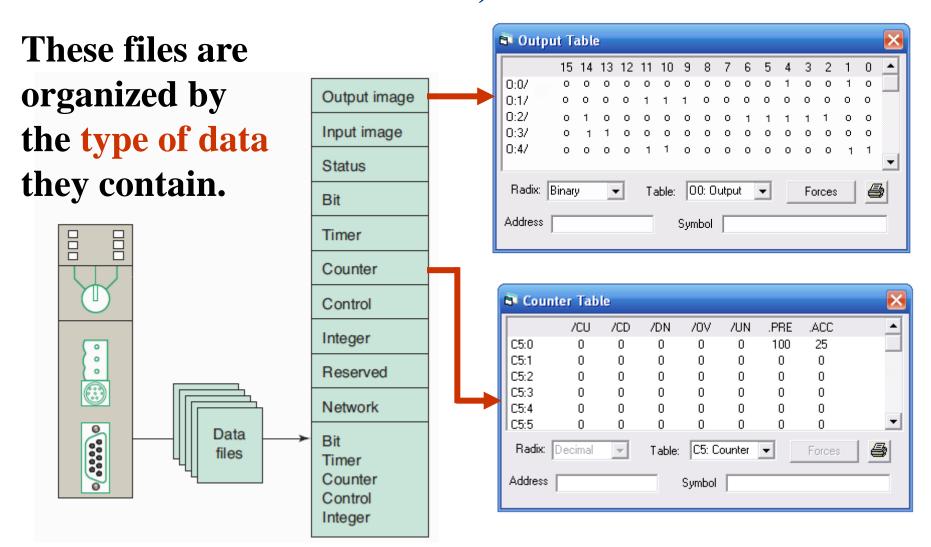

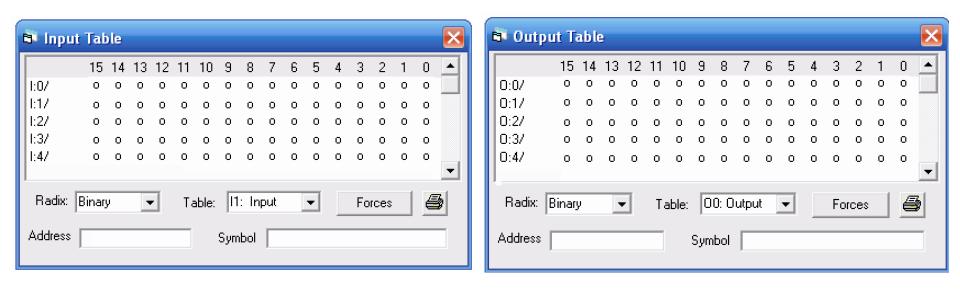

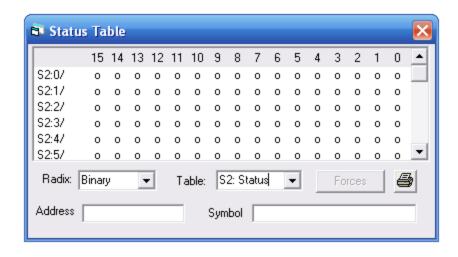

The *Data file* portion of the processor's memory stores input and output status, processor status, the status of various bits, and numerical data.

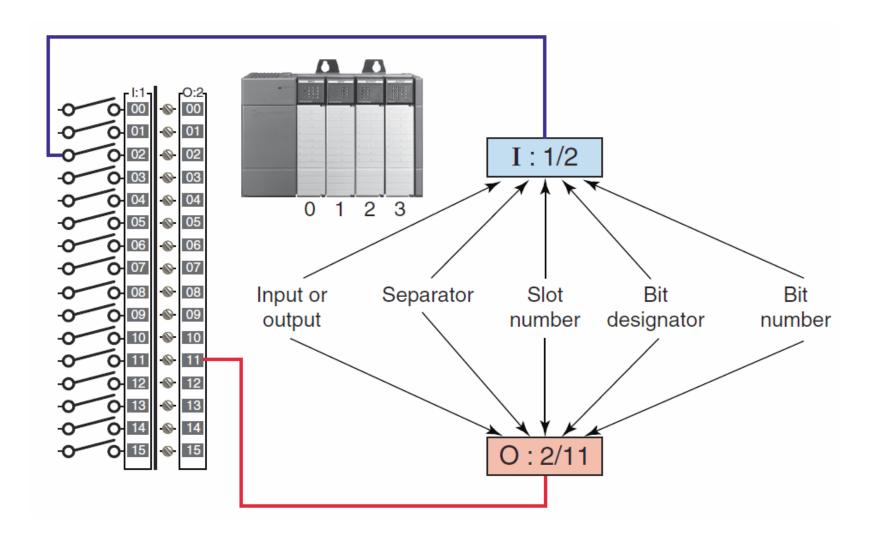

#### I/O address format for the SLC family of PLCs.

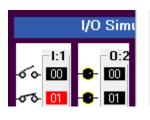

### Simulated I/O addressing format for the *SLC* family of PLCs.

## Memory organization for a *PLC-5* controller.

| Address range    |                                      | Size, in elements  |

|------------------|--------------------------------------|--------------------|

| O:000            |                                      |                    |

| O:037            | Output image file                    | 32                 |

| I:000<br>I:037   | Input image file                     | 32                 |

| S:000            | Processor status                     | 32                 |

| S:031            |                                      |                    |

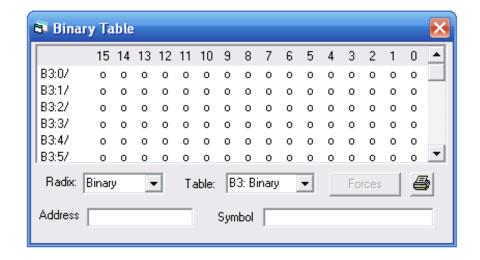

| B3:000           | Bit file                             | 1-1000             |

| B3:999           | Dit file                             | 1-1000             |

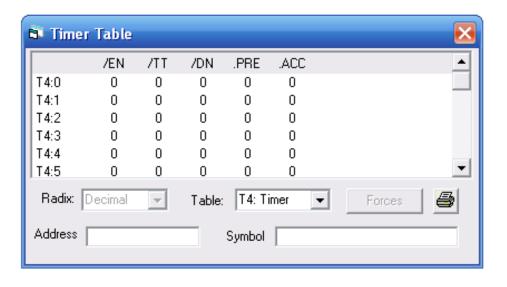

| T4:000           | Timer file                           | 1–1000             |

| T4:999           |                                      |                    |

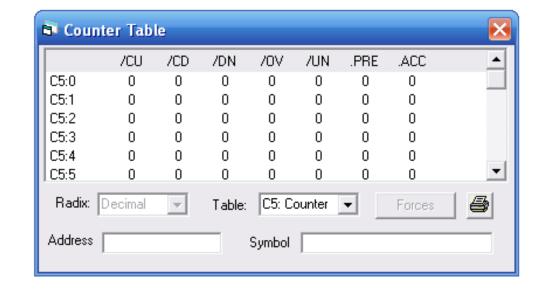

| C5:000           | Counter file                         | 1-1000             |

| C5:999           |                                      |                    |

| R6:000<br>R6:999 | Control file                         | 1–1000             |

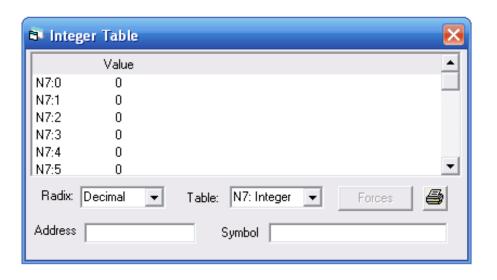

| N7:000           |                                      |                    |

| N7:999           | Integer file                         | 1–1000             |

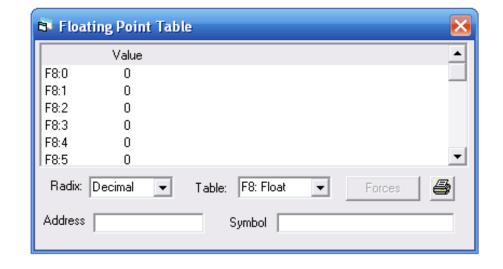

| F8:000           | Floating-point file                  | 1–1000             |

| F8:999           |                                      |                    |

| 1 0.000          | Files to be assigned file nos. 9–999 | 1–1000<br>per file |

### The PLC-5 and SLC 500 store all data in global data tables and are based on 16-bit operations.

You access these data by specifying the address of the data you want.

The addresses in the output data file and the input data file are potential locations for I/O modules mounted in the chassis.

© 2011, The McGraw-Hill Companies, Inc.

The status data file contains information about the processor status

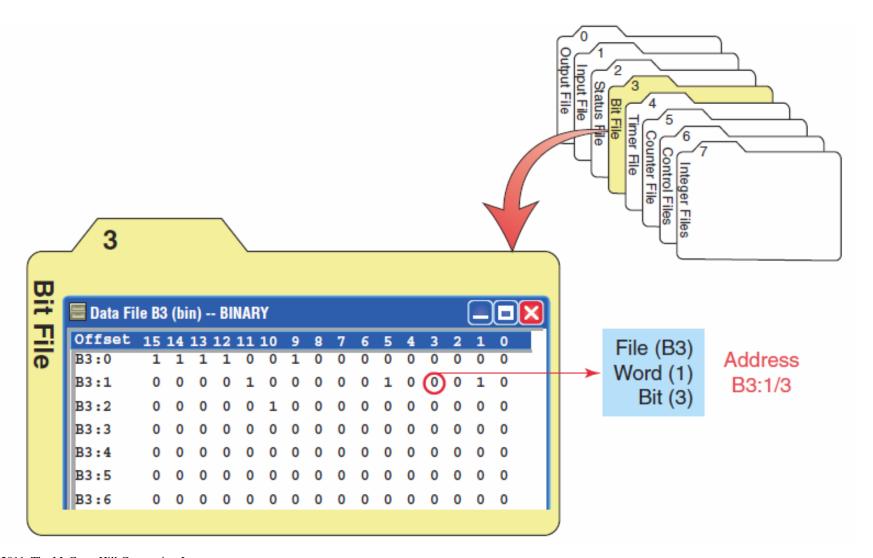

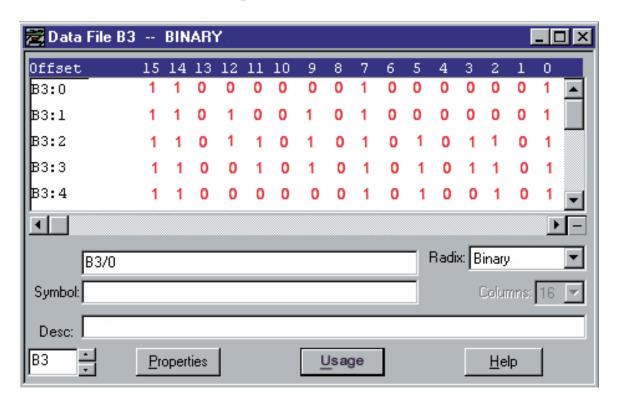

The bit data file stores bit status and frequently serves for storage when using internal outputs.

The timer file stores the timer status and timer data.

The counter file stores the counter status and counter data.

The integer file stores integer data values.

The floating point file can store data that requires a decimal point.

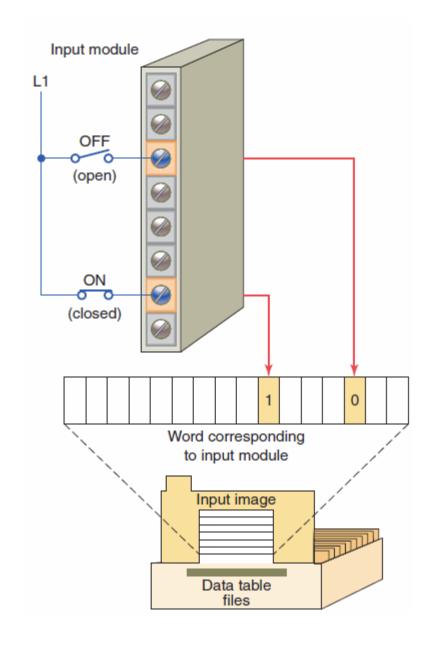

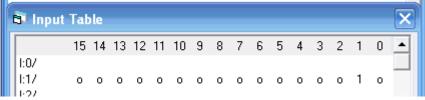

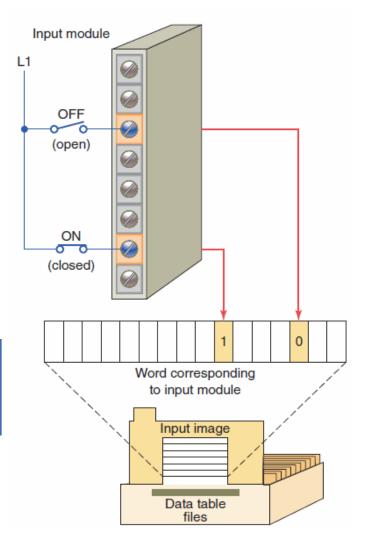

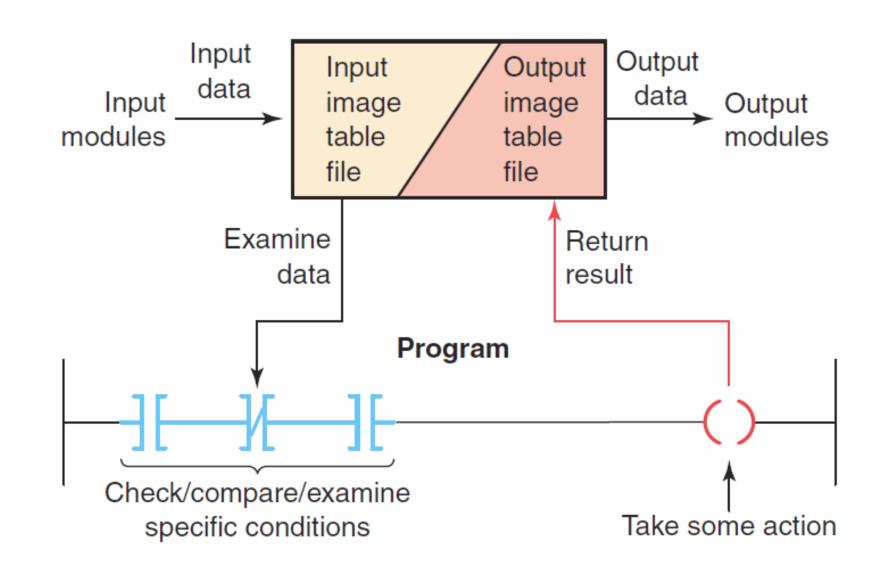

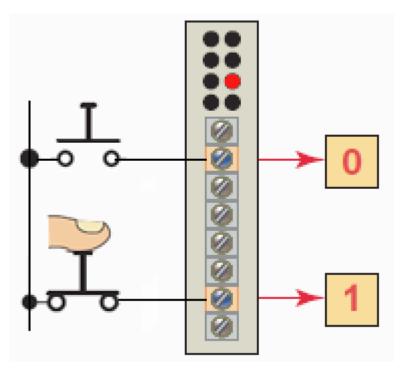

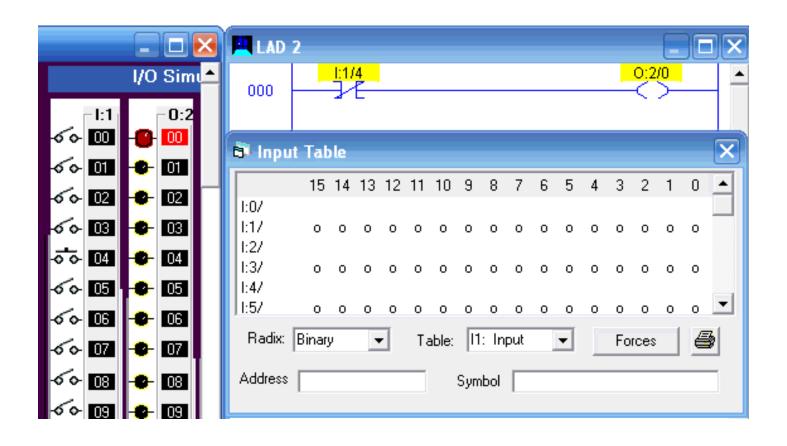

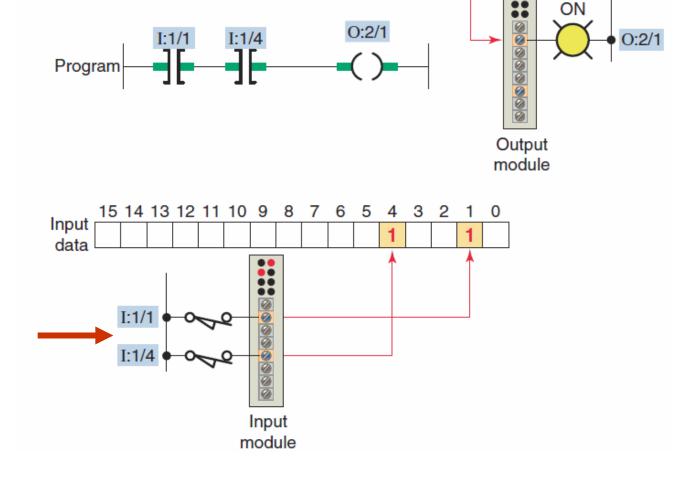

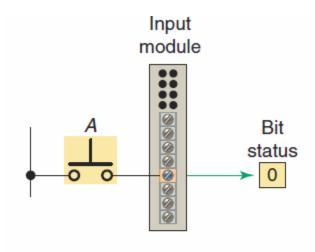

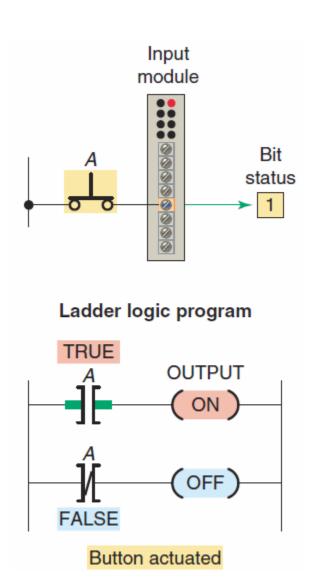

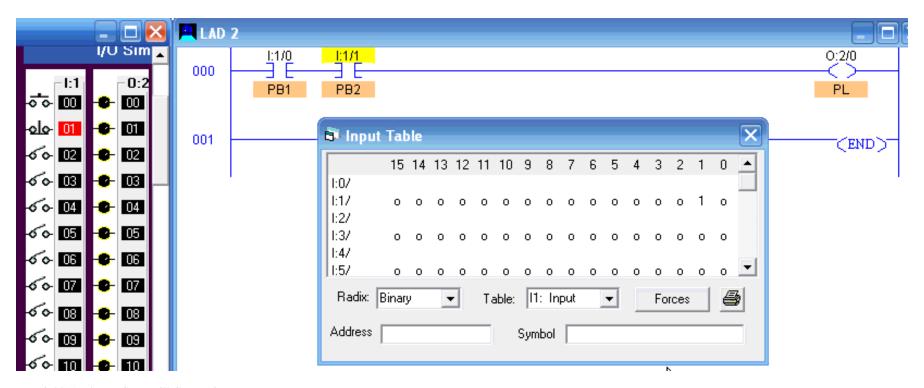

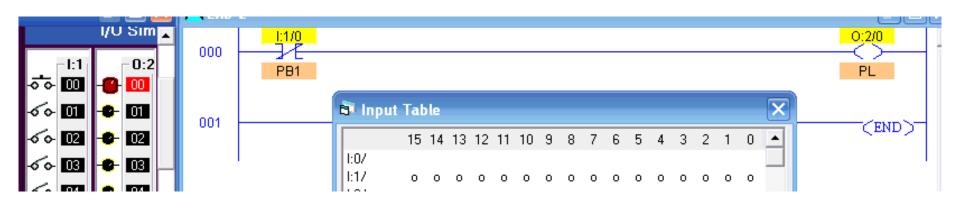

The *input image* table is allocated to storing the *on/off status* of connected discrete inputs.

If the input is on (switch closed), its corresponding bit in the table is set to 1.

If the input is off (switch open), the corresponding bit is cleared, or reset to 0.

# Simulated operation of the *input image* table *on/off status* of connected discrete inputs.

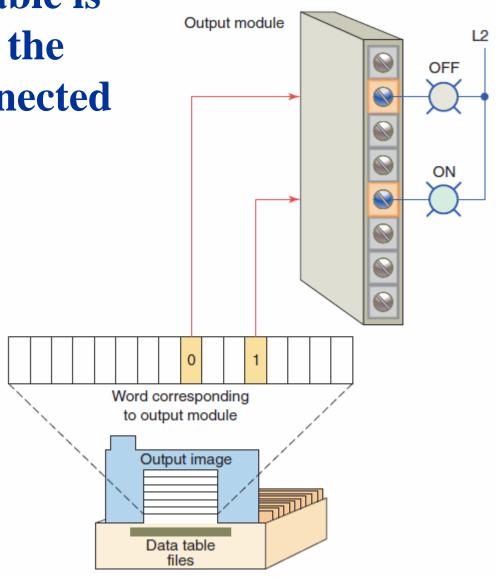

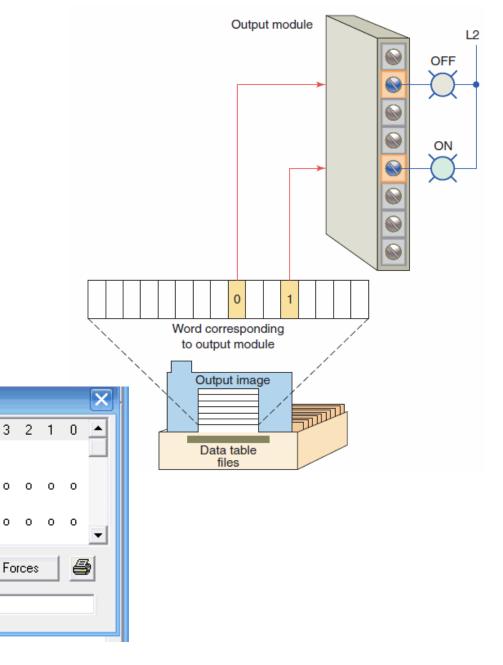

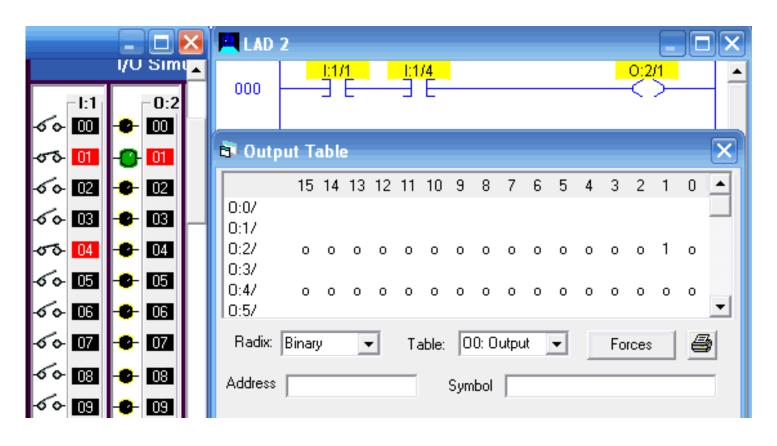

The *output image* table is allocated to storing the on/off status of connected discrete outputs.

If the program calls for an output to be ON, its corresponding bit in the table is set to 1.

If the program calls for an output to be OFF, its corresponding bit in the table is set to 0.

Simulated operation of the *output image* table *on/off status* of connected discrete outputs.

15 14 13 12 11 10 9

00: Output

Symbol

Radix: Binary

Output Table

0:0/

0:17

0:2/

0:3/ 0:4/

0:57

Address

0:2

00

**O** 01

**2** 02

**2** 03

**O** 05

**6** 08

04

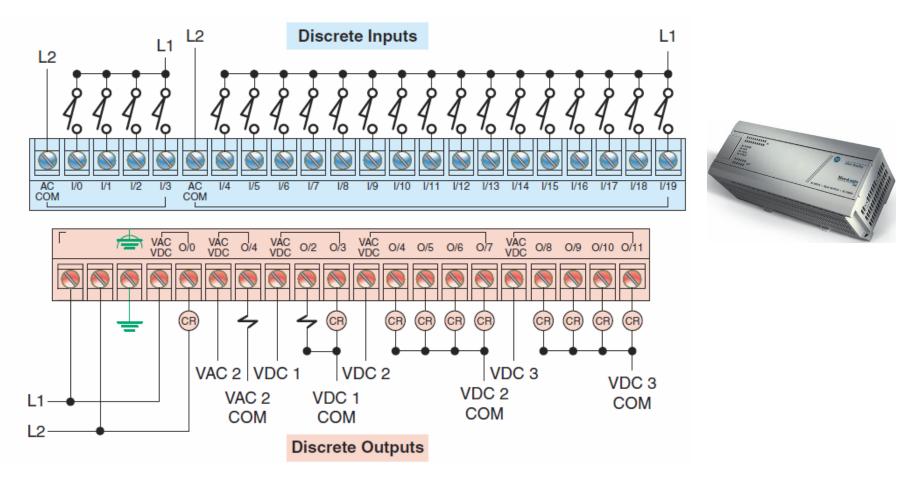

## Typically, *micro PLCs* have a *fixed* number of inputs and outputs.

This controller has 20 discrete inputs with addresses I/0 through I/19 and 12 discrete outputs with addresses O/1 through O/11.  $^{\circ}$  2011, The McGraw-Hill Companies, Inc.

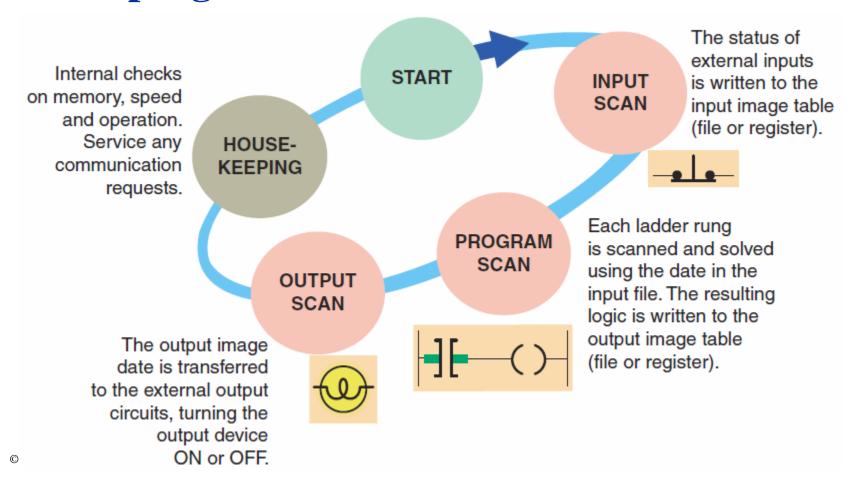

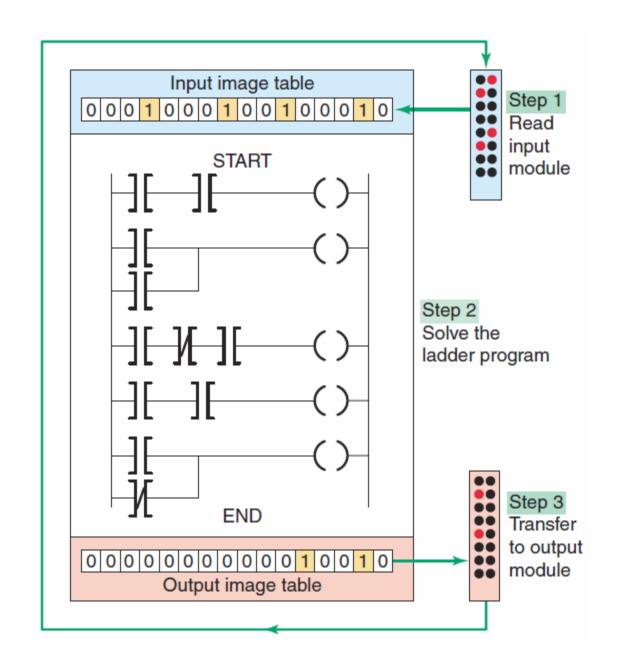

### Program Scan

During each *program scan cycle*, the processor reads all the inputs, takes these values, and energizes or de-energizes the outputs according to the user program.

The *time* it takes to complete a scan cycle is a measure of how fast the controller can *react* to changes in inputs.

If a controller has to react to an input signal that changes states twice during the scan time, it is possible that the PLC will never be able to detect this change.

#### The scan time is a function of:

- The speed of the processor module

- The length of the ladder program

- The type of instructions executed

- The actual ladder true/false conditions

The PLC computes the scan time each time the END instruction is executed.

Typical scan time data include the maximum scan time and the last scan time.

#### Overview of the data flow during the scan process.

#### Scan process applied to a single rung program.

Scan process applied to a multiple rung program.

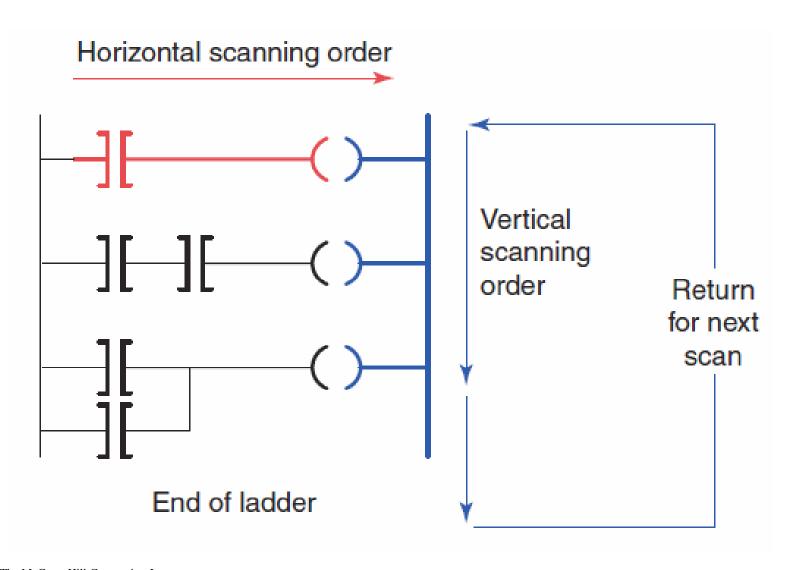

#### Vertical versus horizontal scan patterns.

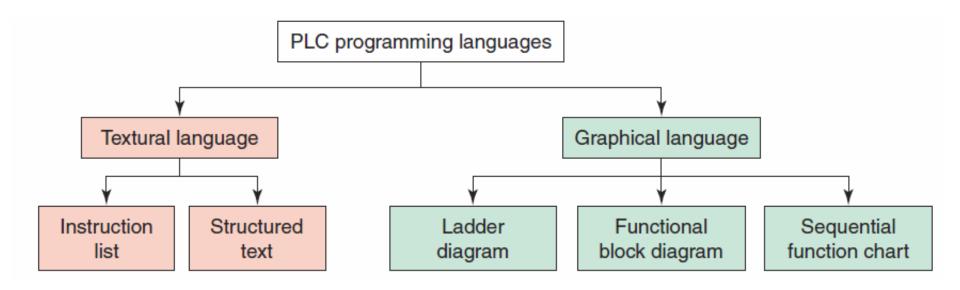

## PLC Programming Languages

#### PLC programming language refers to the method by which the user communicates information to the PLC.

#### Standard PLC programming languages

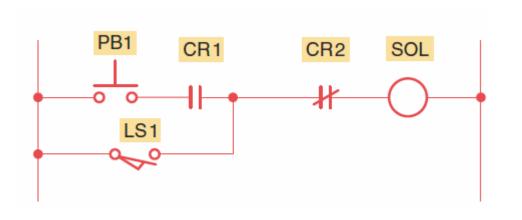

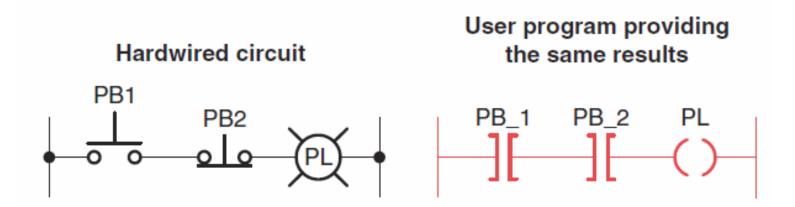

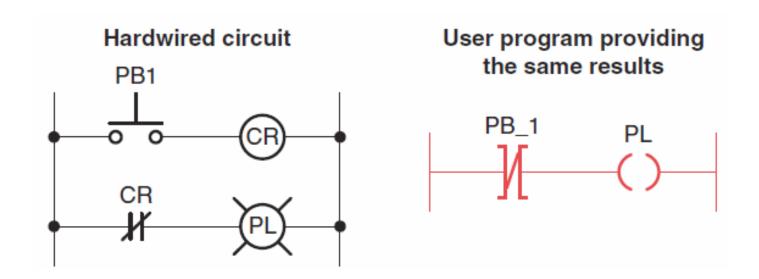

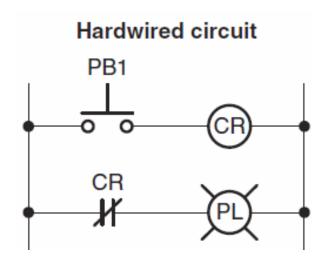

## Ladder diagram language is the most commonly used PLC language and is designed to mimic hardwired relay logic.

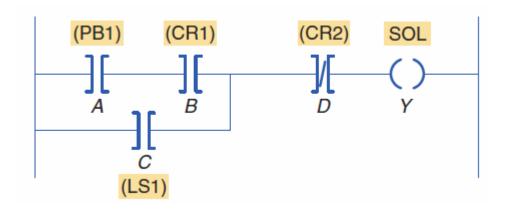

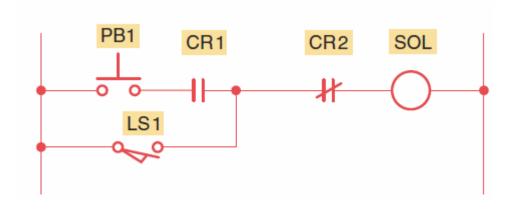

Hardwired relay control circuit

**Equivalent ladder diagram program**

## Instruction list programming language consists of a series of instructions that refer to the basic AND, OR, and NOT logic gate functions.

Hardwired relay control circuit

START PB1

AND CR1

OR LS1

AND NOT CR2

OUT SOL

**Equivalent instruction list program**

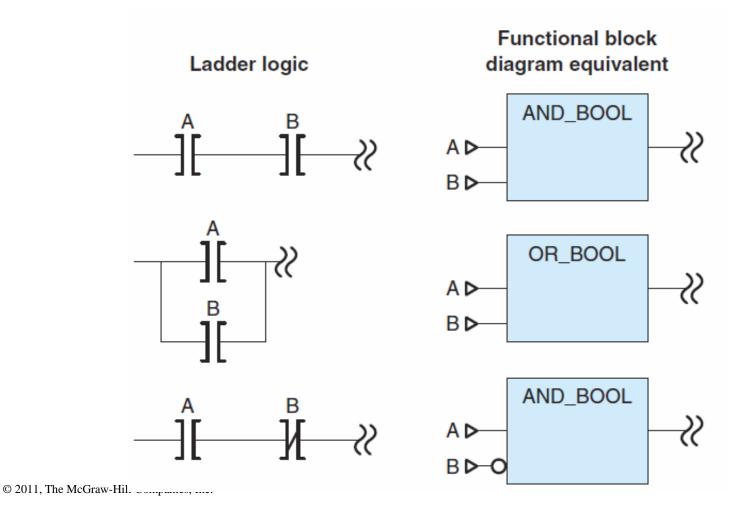

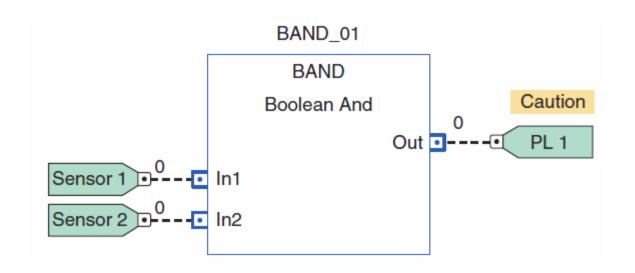

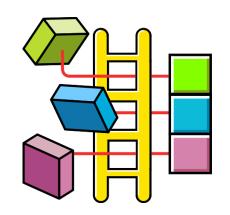

## Functional block diagram programming uses instructions that are programmed as blocks wired together to accomplish certain functions.

## Ladder diagram and functional block diagram programming used to produce the same logical output.

Equivalent function block diagram.

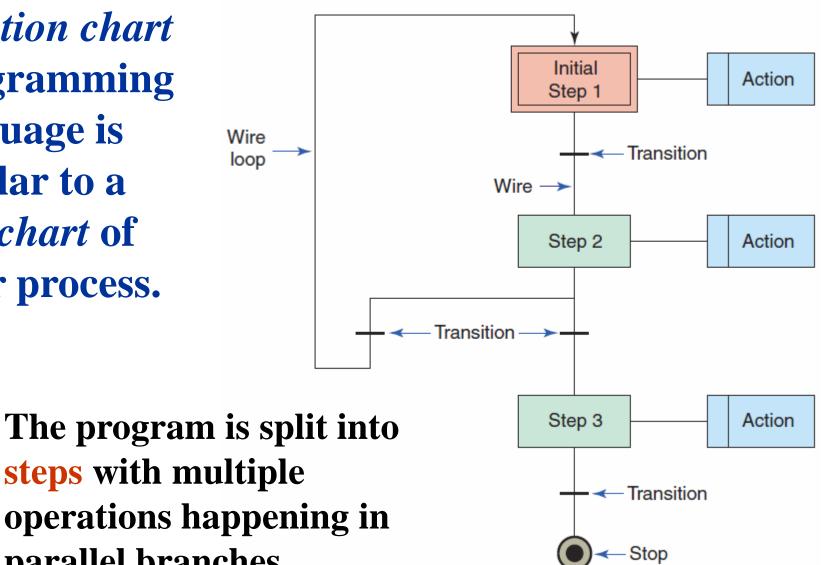

Sequential function chart programming language is similar to a flowchart of your process.

steps with multiple operations happening in parallel branches.

## Structured text is a high level language primarily used to implement more complex procedures.

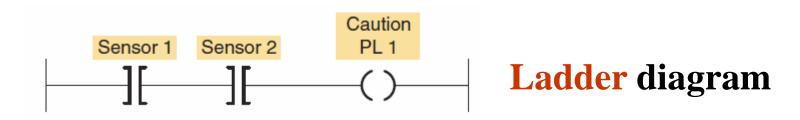

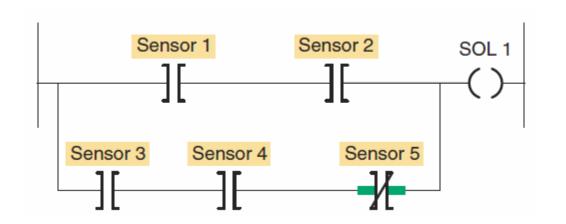

Ladder diagram

```

IF Sensor_1 AND Sensor_2 THEN

SOL_1 := 1;

ELSEIF Sensor_3 AND Sensor_4 AND NOT Sensor_5 THEN

SOL_1 := 1;

END_IF;

```

Equivalent structured text program.

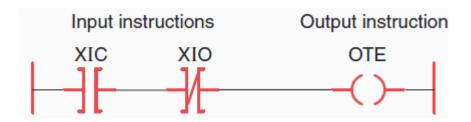

### Relay Type Instructions

The ladder diagram language is a *symbolic* set of instructions used to create the controller program.

Representations of contacts and coils are the basic symbols of the logic ladder diagram instruction set.

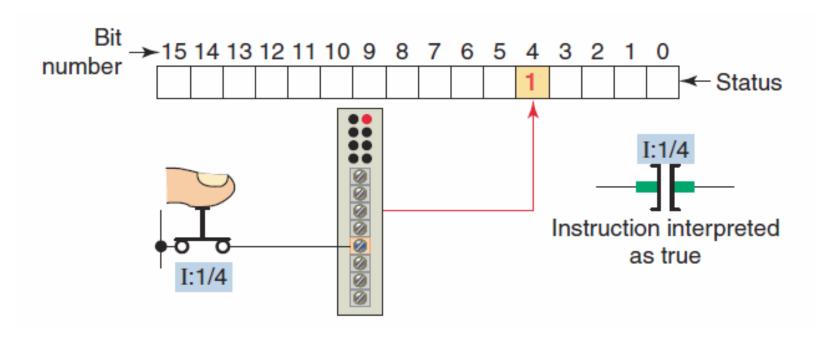

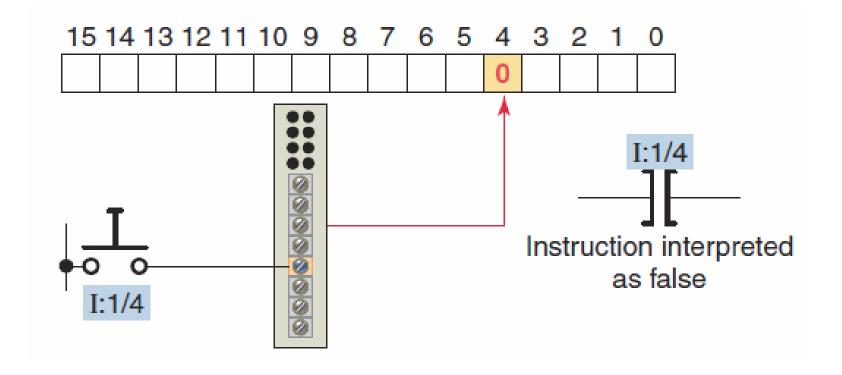

# The Examine If Closed (XIC) instruction looks and operates like a normally open relay contact.

Associated with each XIC instruction is a memory bit linked to the status of an input device or an internal logical condition in a rung.

The memory bit is set to 1 or 0 depending on the status of the input.

A 1 corresponds to a true status or on condition.

If the instruction memory bit is a 1 (true) this instruction will allow rung continuity through itself, like a closed relay contact.

#### A 0 corresponds to a false status or off condition.

If the instruction memory bit is a 0 (false) this instruction will not allow rung continuity through itself and will assume a normally open state just like an open relay contact.

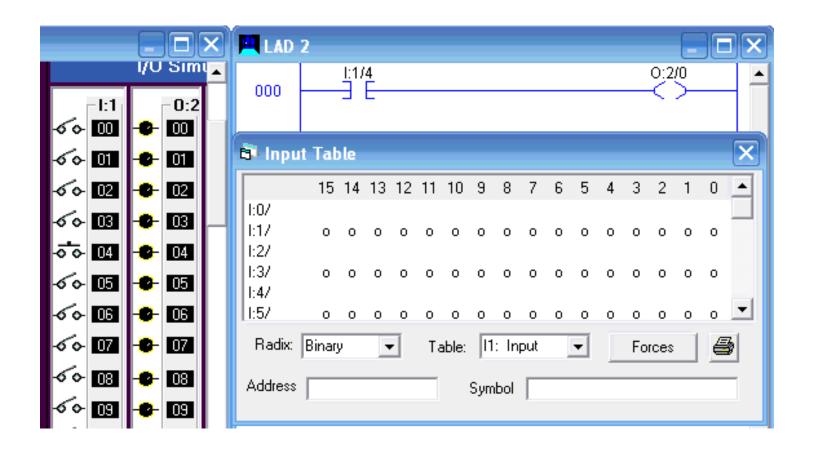

## Simulated *Examine If Closed (XIC)* instruction operation.

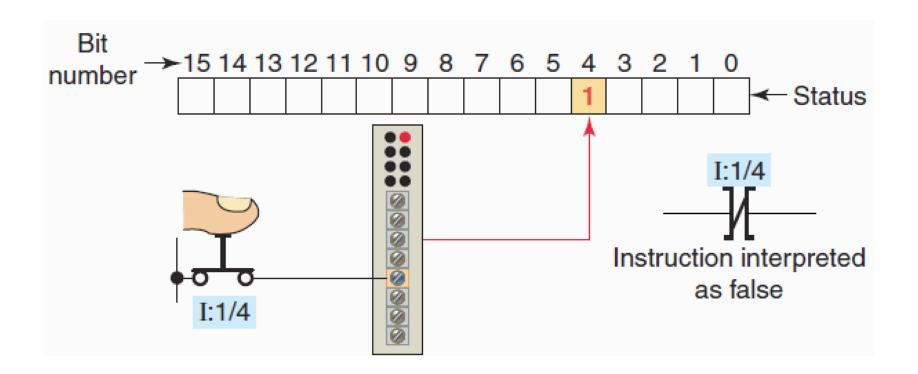

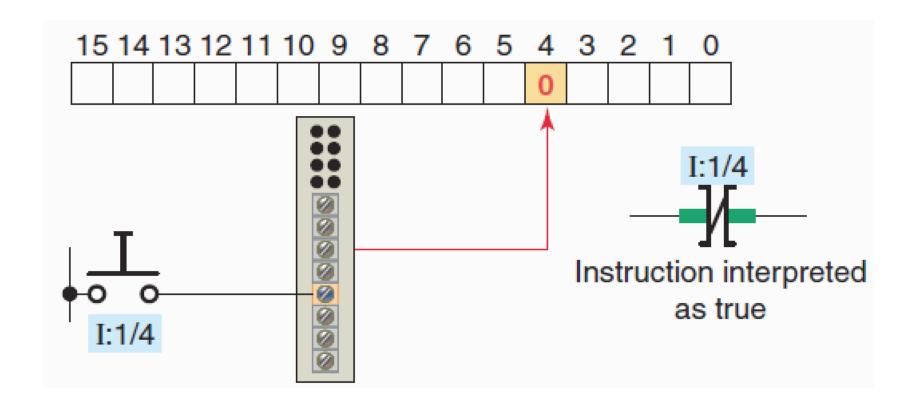

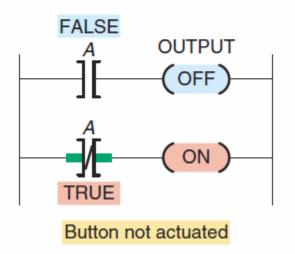

The Examine If Open (XIO) instruction looks and operates like a normally closed relay contact.

Examine if open (XIO)

Examine-off

This instruction asks the PLC's processor to examine if the contact is open.

It does this by examining the bit at the memory location specified by the address for a 0 or 1.

As with any other input the memory bit is set to 1 or 0 depending on the status of the input. A 1 corresponds to a true status or on condition.

The instruction is interpreted as false when the bit is 1 and will not allow rung continuity through itself.

### A 0 corresponds to a off condition.

The instruction is interpreted as true when the bit is 0 and will not allow rung continuity through itself.

# Simulated *Examine If Open (XIO)* instruction operation.

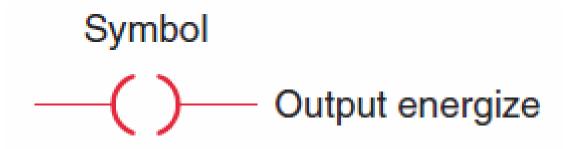

The Output Energize (OTE) instruction looks and operates like a relay coil.

This instruction signals the PLC to energize (switch on) or de-energize (switch off) the output.

The instruction is associated with a memory bit that energizes the output when set to 1 and de-energizes the output when reset to 0.

OTE instruction is set to 1 to — energize the output.

Output

data

A true logic path is established by the input instructions in the rung.

# Simulated *Output Energize (OTE)* instruction operation.

## Action of the field device and PLC bit.

Ladder logic program

A signal present makes the **NO** bit (1) true; a signal absent makes the NO bit (0) false. The reverse is true for an NC bit.

## Simulated operation of the field input device and the PLC bit.

The main function of the ladder logic diagram program is to *control outputs* based on *input* conditions.

Each contact or coil symbol is referenced with an address that identifies what is being evaluated and what is being controlled.

The same contact instruction can be used throughout the program whenever that condition needs to be evaluated.

## For an output to be activated or energized, at least one left-to-right *true logical path* must exist.

When logical continuity exists in at least one path, the rung condition and Output Energize instruction are said to be true.

### Simulated operation of logic continuity.

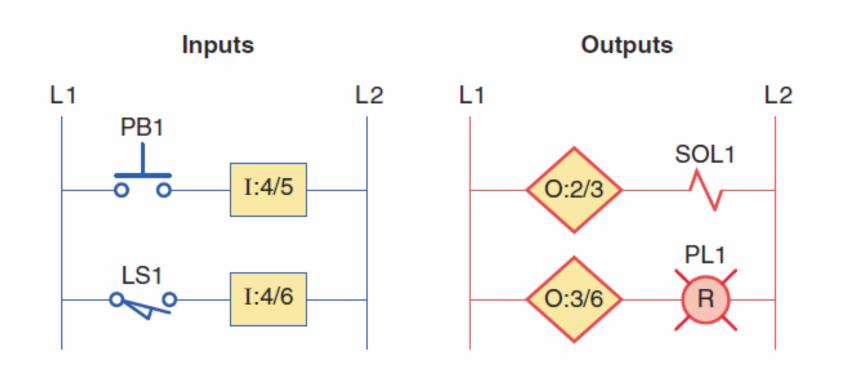

## Instruction Addressing

# To complete the entry of a relay-type instruction, you must assign an *address* to each instruction.

### Simulated operation of instruction addressing.

## The assignment of an I/O address can be included in the I/O connection diagram.

Inputs and outputs are typically represented by squares and diamonds, respectively.

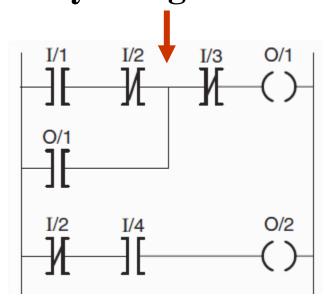

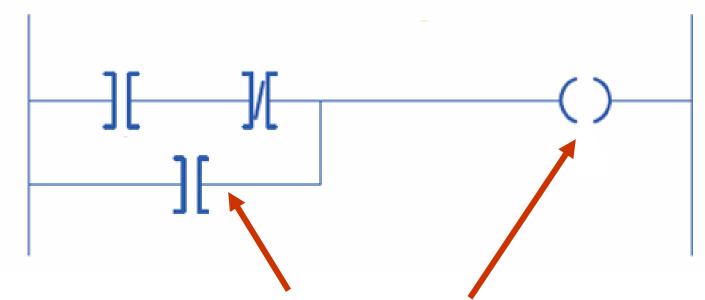

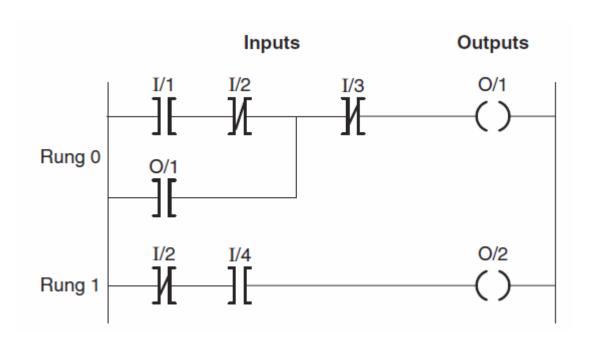

## **Branch Instructions**

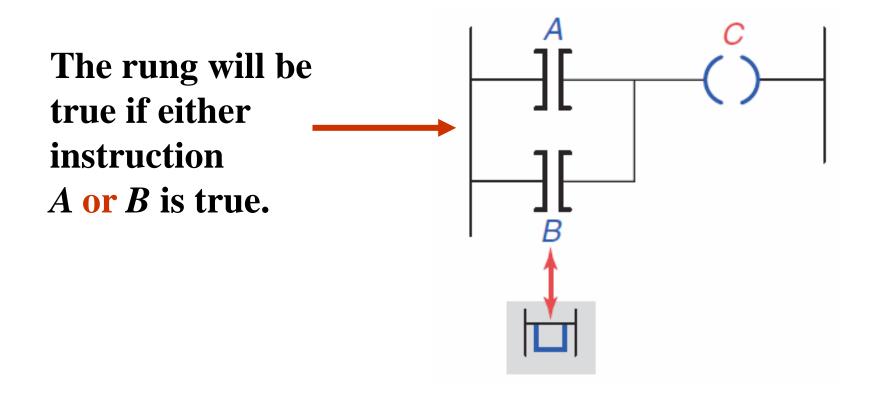

## Branch instructions are used to create parallel paths of input condition instructions.

### Simulated branch instructions.

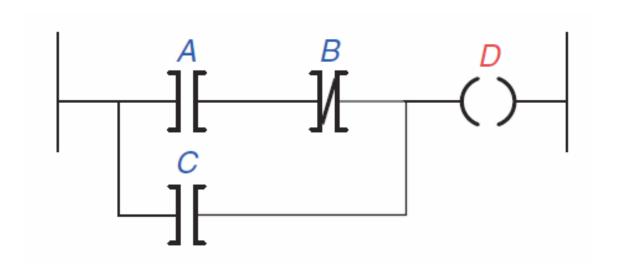

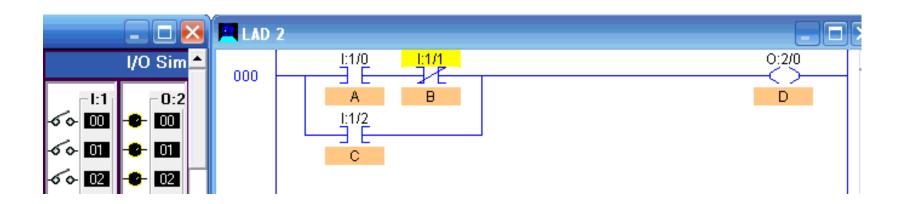

## Parallel branches can be used to allow more than one *combination* of input conditions.

Either A and not B, or C provides logical continuity and energizes output D.

# Simulated program, either A and not B, or C provides logical continuity and energizes output D.

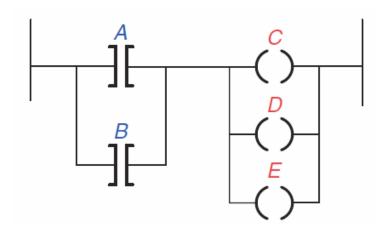

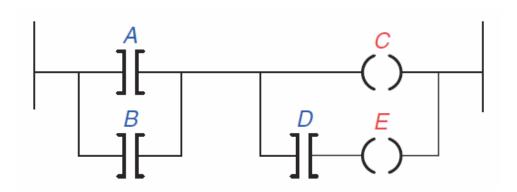

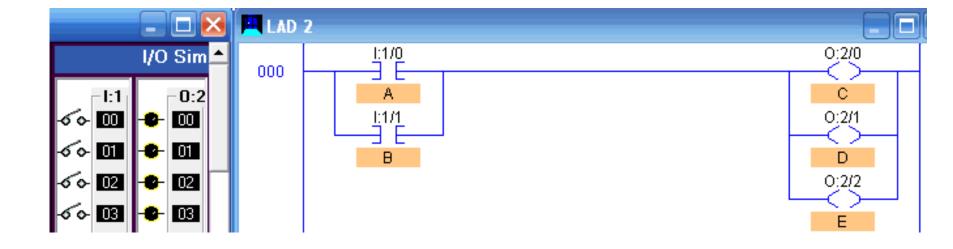

# Output branching allows a true logic path to control multiple outputs

Either A or B provides a true logical path to all three output instructions: C, D, and E.

Additional input instructions can be programmed in the output branches.

# Simulated program, either A or B provides a true logical path to all three output instructions: C, D, and E.

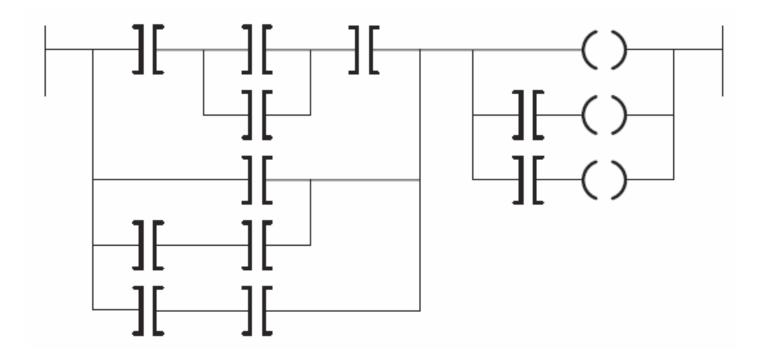

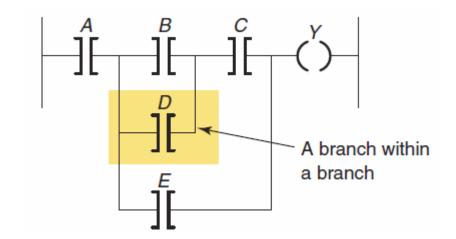

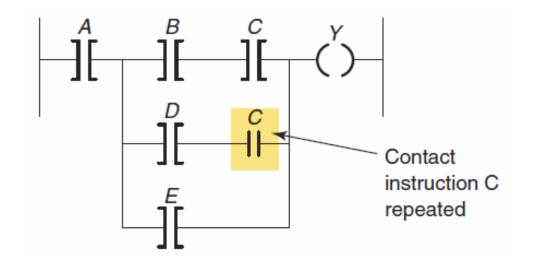

Input and output branches can be *nested* to avoid redundant instructions and to speed up processor scan time.

A nested branch starts or ends within another branch.

In some PLC models, the programming of a nested branch cannot be done directly.

It is possible, however, to program a logically equivalent branching condition.

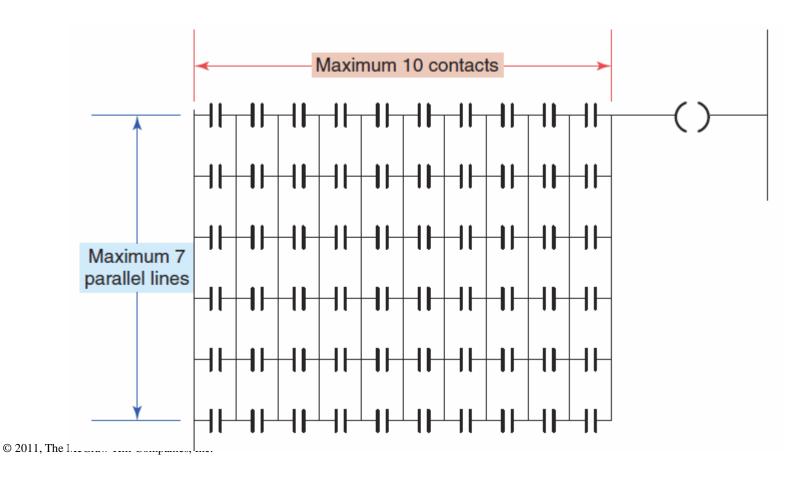

There may be *limitations* to the number of *series* contact instructions that can be included in one rung of a ladder diagram as well as limitations to the number of *parallel branches*.

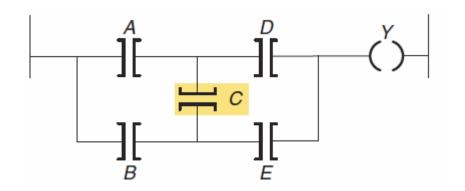

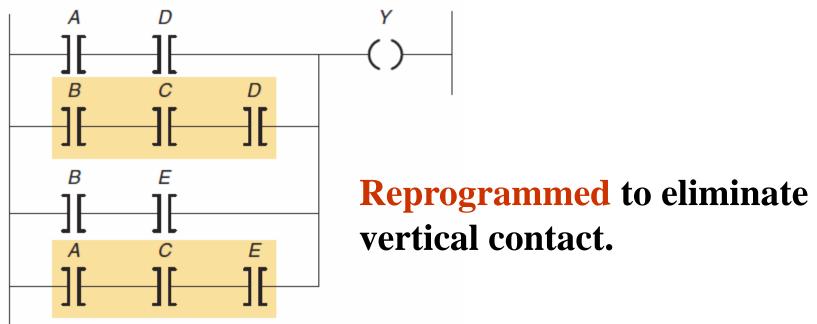

# The PLC will not allow for programming of vertical contacts.

Boolean equation: Y = (AD) + (BCD) + (BE) + (ACE)

© 2011, The McGraw-Hill Companies, Inc.

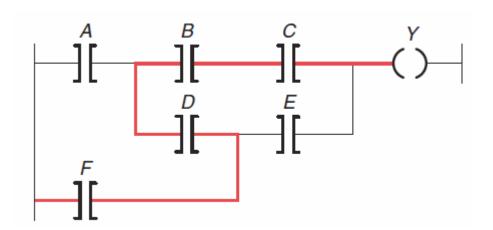

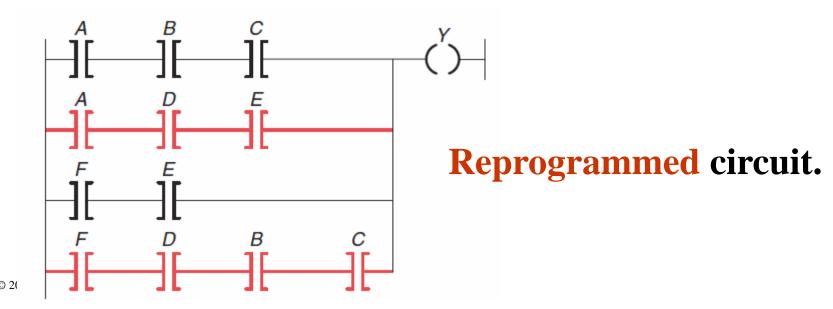

The processor examines the ladder logic rung for logic continuity from left to right.

If programmed as shown, contact combination FDBC would be ignored.

Boolean equation: Y = (ABC) + (ADE) + (FE) + (FDBC)

# Internal Relay Instructions

## An internal output does not directly control an output field device.

The advantage of using internal outputs is that there are many situations in which an output instruction is required in a program but no physical connection to a field device is needed.

© 2011, The McGraw-Hill Companies, Inc.

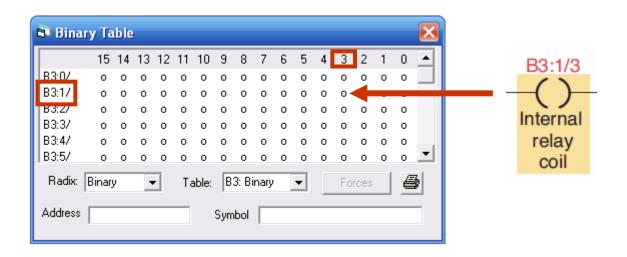

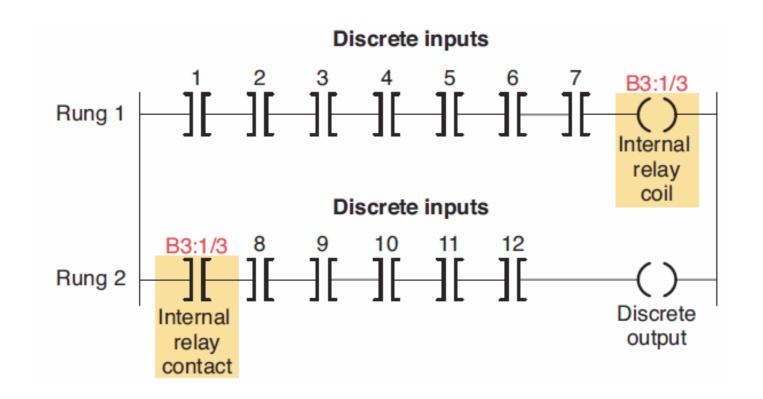

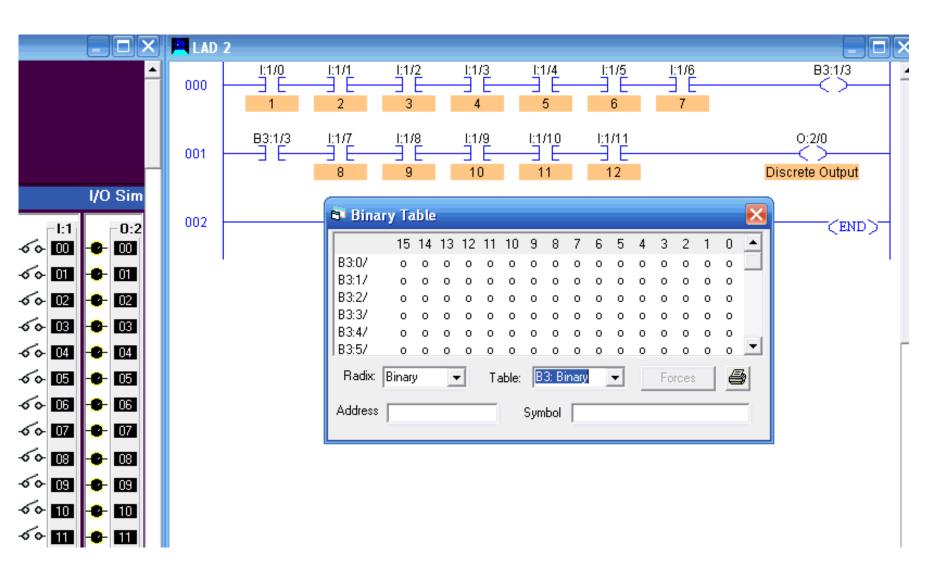

## SLC 500 controllers use bit file B3 for internal bit addressing.

## Internal relay used for a program that requires more series contacts than the rung allows.

This PLC allows for only 7 series contacts when 12 are actually required for the programmed logic.

# Simulated internal relay program.

# Programming Examine If Closed and Examine If Open Instructions

## **Examine If Closed (XIC) instruction**

Both the NO and the NC pushbuttons are represented in the program by the Examine If Closed instruction.

The normal state of the field input device (NO or NC) does not matter to the controller.

What matters is that contacts need to closed to energize the output.

## Simulated Examine If Closed (XIC) instruction

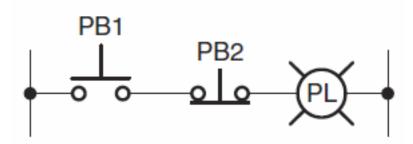

#### Hardwired circuit

# **Examine If Open (XIO) instruction**

The pushbutton is represented in the user program by an Examine If Open instruction.

This is because the rung must be true when the external pushbutton is open and false when the pushbutton is closed.

# Simulated Examine If Open (XIO) instruction

# The logic states (0 or 1) indicate whether an instruction is true or false and is the basis of controller operation.

|                          | The status of the instruction is |                              |                        |  |

|--------------------------|----------------------------------|------------------------------|------------------------|--|

| If the data table bit is | XIC<br>EXAMINE IF CLOSED         | XIO<br>EXAMINE IF OPEN       | OTE<br>OUTPUT ENERGIZE |  |

|                          | -][-                             | <del>-</del> }/ <del>-</del> | <del>-()-</del>        |  |

| Logic 0                  | False                            | True                         | False                  |  |

| Logic 1                  | True                             | False                        | True                   |  |

The time aspect relates to the repeated scans of the program, wherein the input table is updated with the most current status bits.

|                          | Instruction outcome |       |               |

|--------------------------|---------------------|-------|---------------|

| Time                     | XIC                 | XIO   | OTE           |

| t <sub>1</sub> (initial) | False               | True  | False         |

| t <sub>2</sub>           | True                | True  | Goes true     |

| <i>t</i> <sub>3</sub>    | True                | False | Goes false    |

| <i>t</i> <sub>4</sub>    | False               | False | Remains false |

| Input b |     |     |

|---------|-----|-----|

| XIC     | XIO | OTE |

| 0       | 0   | 0   |

| 1       | 0   | 1   |

| 1       | 1   | 0   |

| 0       | 1   | 0   |

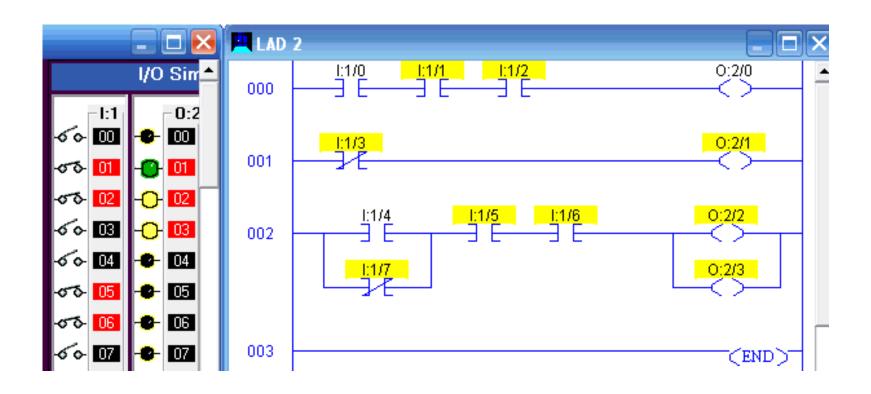

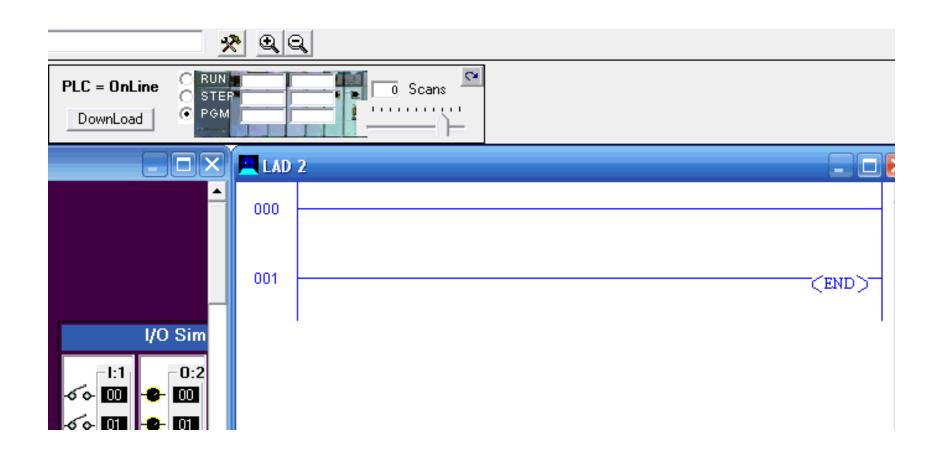

# Entering The Ladder Diagram

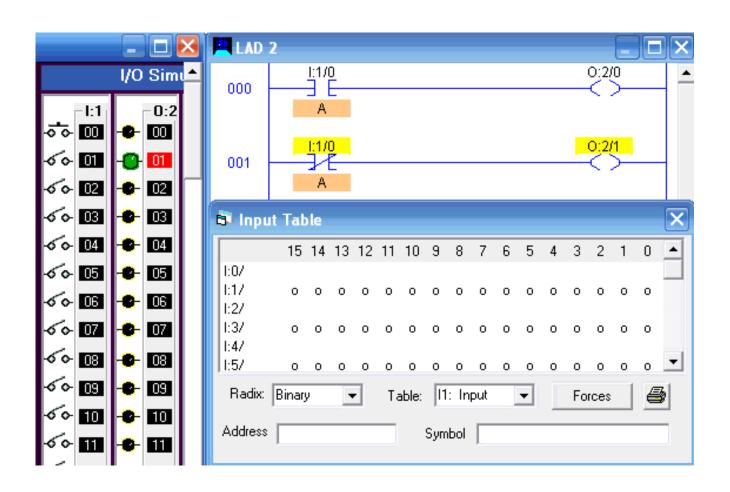

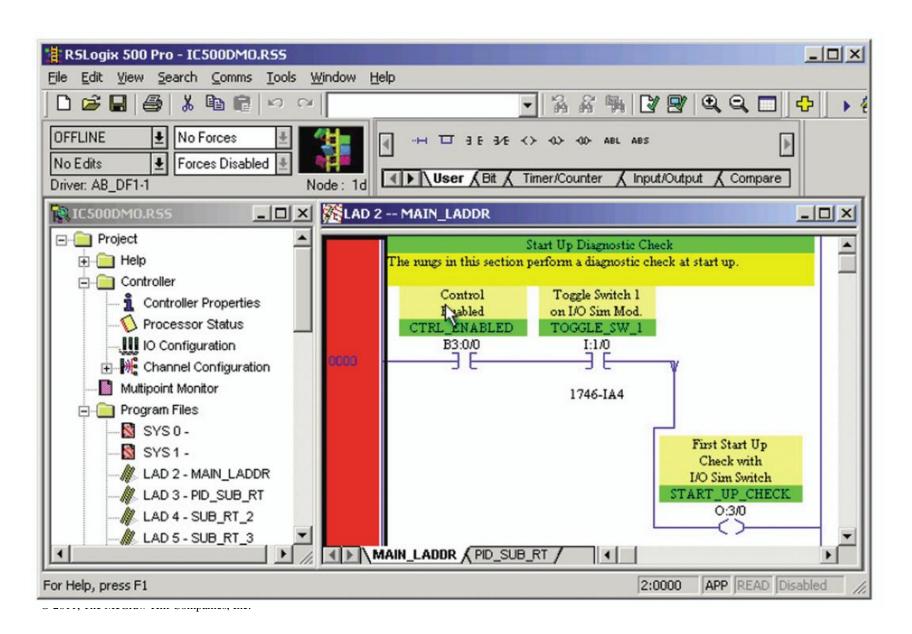

Allen-Bradley's RSLogix software packages are windows programming packages used to develop ladder logic programs.

Software, in various versions, can be used to program the PLC-5, SLC 500, ControlLogix, and MicroLogic family of processors.

A personal computer is most often used and is adapted to the particular PLC model through the use of the relevant programmable controller software.

© 2011, The McGraw-Hill Companies, Inc.

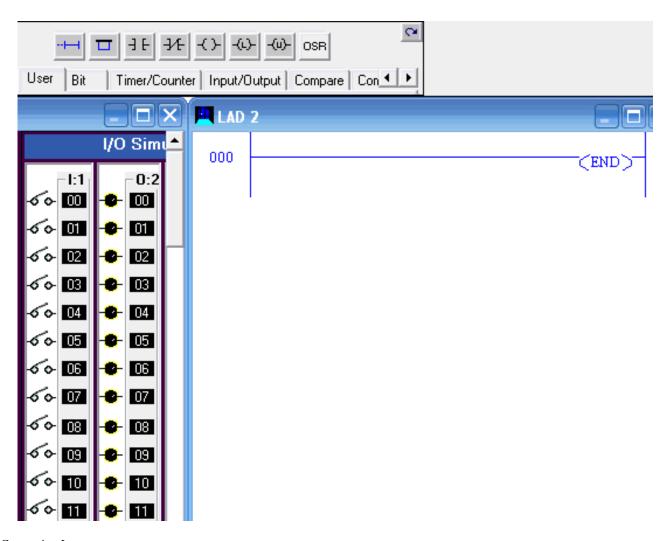

## RSLogix SLC 500 main window.

#### Instruction toolbar with bit instructions selected.

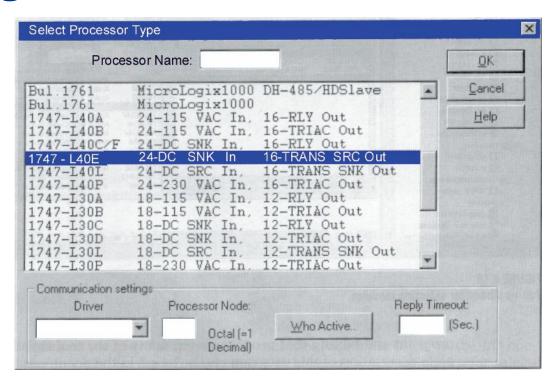

To place an instruction on a rung, click its icon on the toolbar and simply drag the instruction straight off the toolbar onto the rung of the ladder. The programming software needs to know what *processor* is being used in conjunction with the user program.

The Select Processor Type screen contains a list of the different processors that the RSLogix software can program. Companies, Inc.

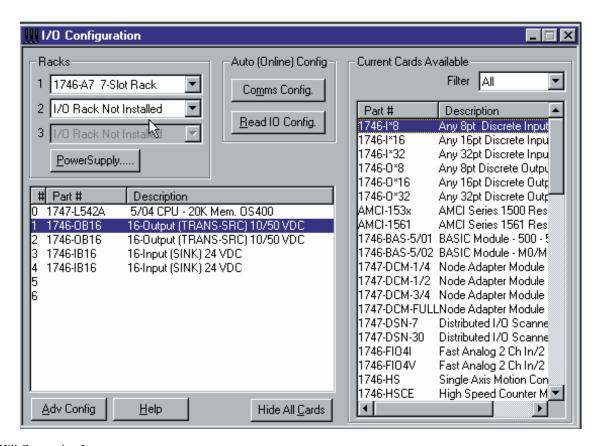

The *I/O Configuration screen* lets you double click or drag-and-drop a module from an all-inclusive list to assign it to a slot in your configuration.

Data File screens contain data that are used in conjunction with ladder program instructions and include input and output files as well as timer, counter, integer, and bit files.

The bit file **B3** is used for internal relays.

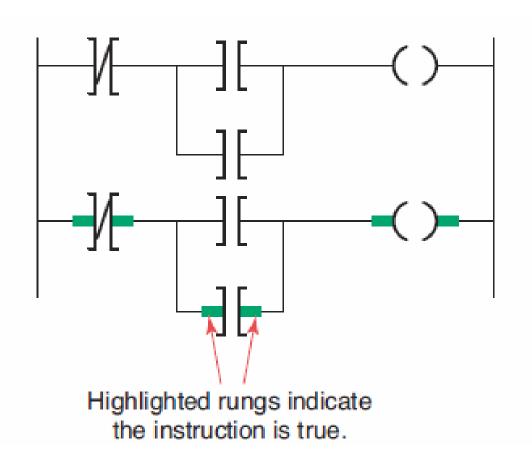

# Relay ladder logic is a *graphical* programming language designed to closely represent the appearance of a wired relay system.

The logic is apparent from the highlighting which identifies the logic state of contacts in real time and which rungs have logic continuity.

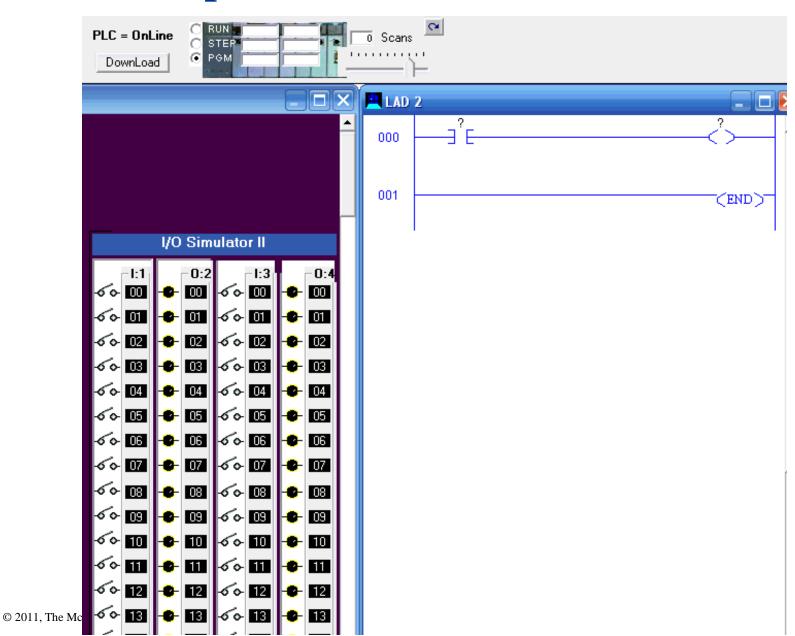

# **Modes Of Operation**

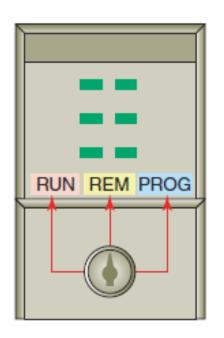

A processor has basically two modes of operation: the *program mode* and some variation of the *run mode*.

A three-position keyswitch may be used to select different processor modes of operation.

The program mode is used to enter a new program, edit or update an existing program, upload files and download files.

The run mode is used to execute the user program.

The test mode is used to operate or monitor the user program without energizing any outputs.

The remote position allows the PLC to be remotely changed between program and run mode by a personal computer connected to the PLC processor.